python副业

鸿蒙系统

ROS

Tableau

openssl

sklearn

HTML5期末考核大作业

iVX低代码平台

按键

skill command

保险

手机浏览器

支持向量机

三星线刷

C++11

知识产权

社交媒体

教程

模板方法模式

Security

数字IC

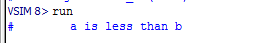

2024/4/11 17:14:27【数字IC/FPGA】Verilog中的递归调用

参考文章 在Verilog2001中,模块的递归调用是可能的,引用下面的一段话(出自上面的参考文章)

Many designers think that recursive techniques cannot be applied to hardware design. I’m not really sure where this misconception comes from. While it is true that i…

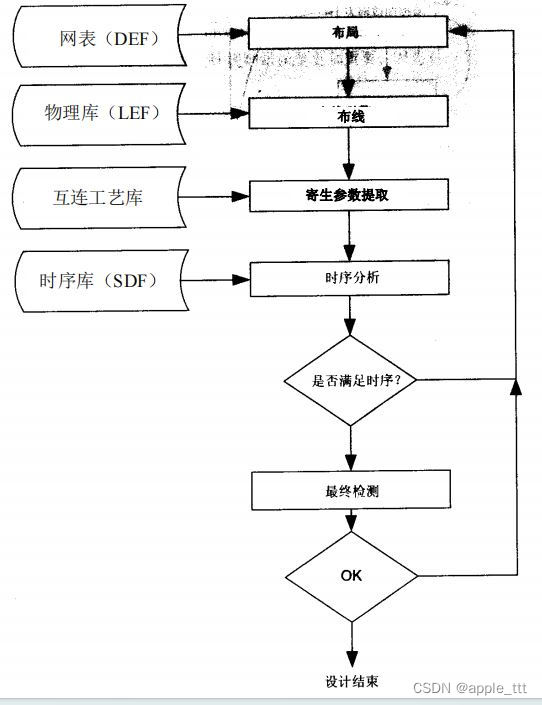

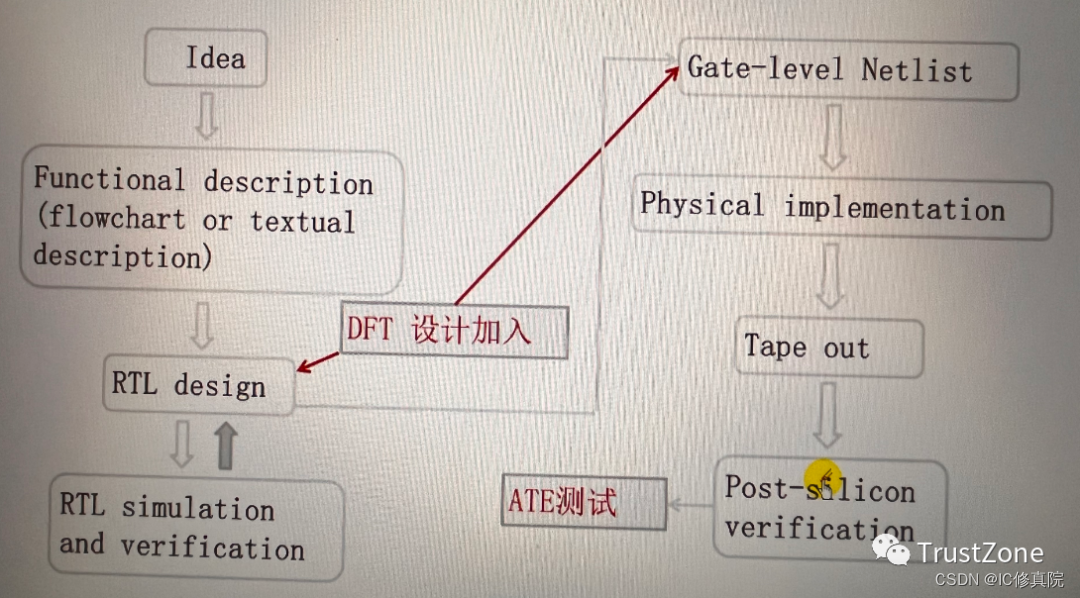

数字IC丨后端设计是个啥?

最近的私信咨询里,很多同学分不清数字IC设计前端和后端的区别,前端设计似乎很容易理解,简单来说就是敲代码的,只不过没有用C和python,用的是硬件描述语言Verilog。

但一说到后端设计,很多同学就懵了&#…

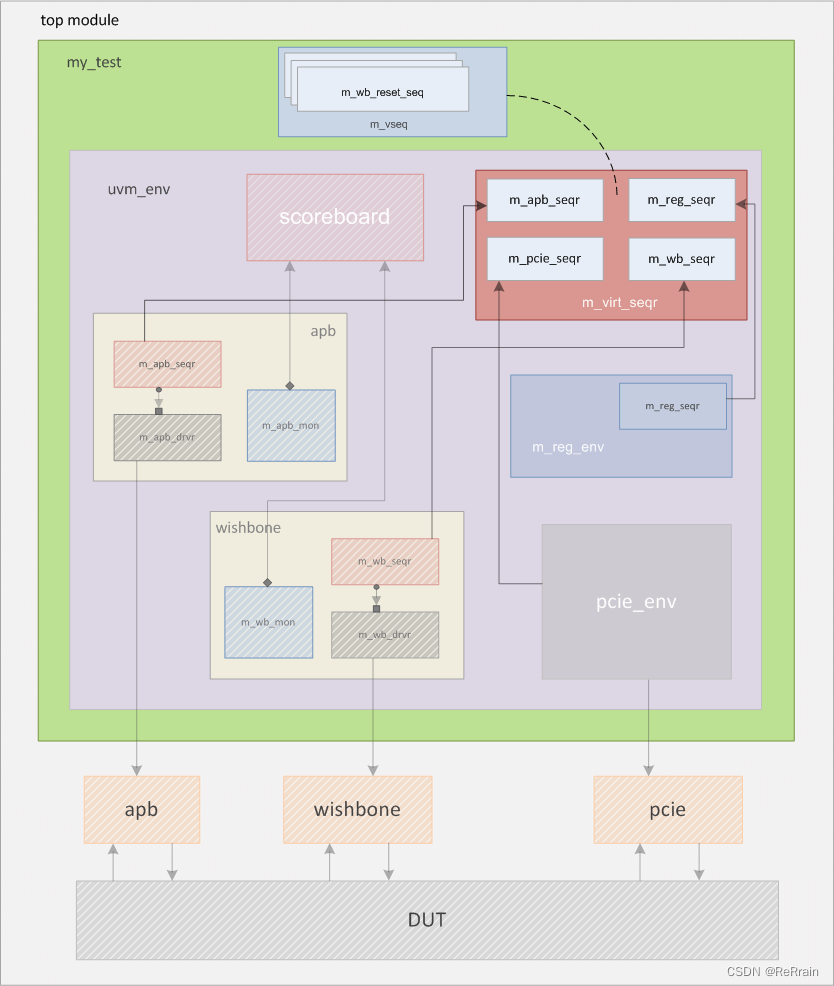

【从零开始学习 UVM】6.5、UVM 激励产生 —— UVM Virtual Sequence【重要】

文章目录 使用virtual sequencer不使用virtual sequencervirtual sequence是一个容器,用于在环境中的virtual sequencer上启动多个sequence。

这个virtual sequence通常由一个具有对真实sequencers句柄的virtual sequencers执行。

需要virtual sequence的原因是当您需要在不…

Aurora 8B/10B

目录 1. Overview2. Feature List2. Block Diagram3. PDU Transmission Procedure3.1. User InterfaceFraming InterfaceStreaming Interface 3.2. Clock Compensation3.3. Aurora 8B/10B Frame Gen3.4. 8B/10B Transmission Code 4. PDU Reception Procedure5. Flow Control5.…

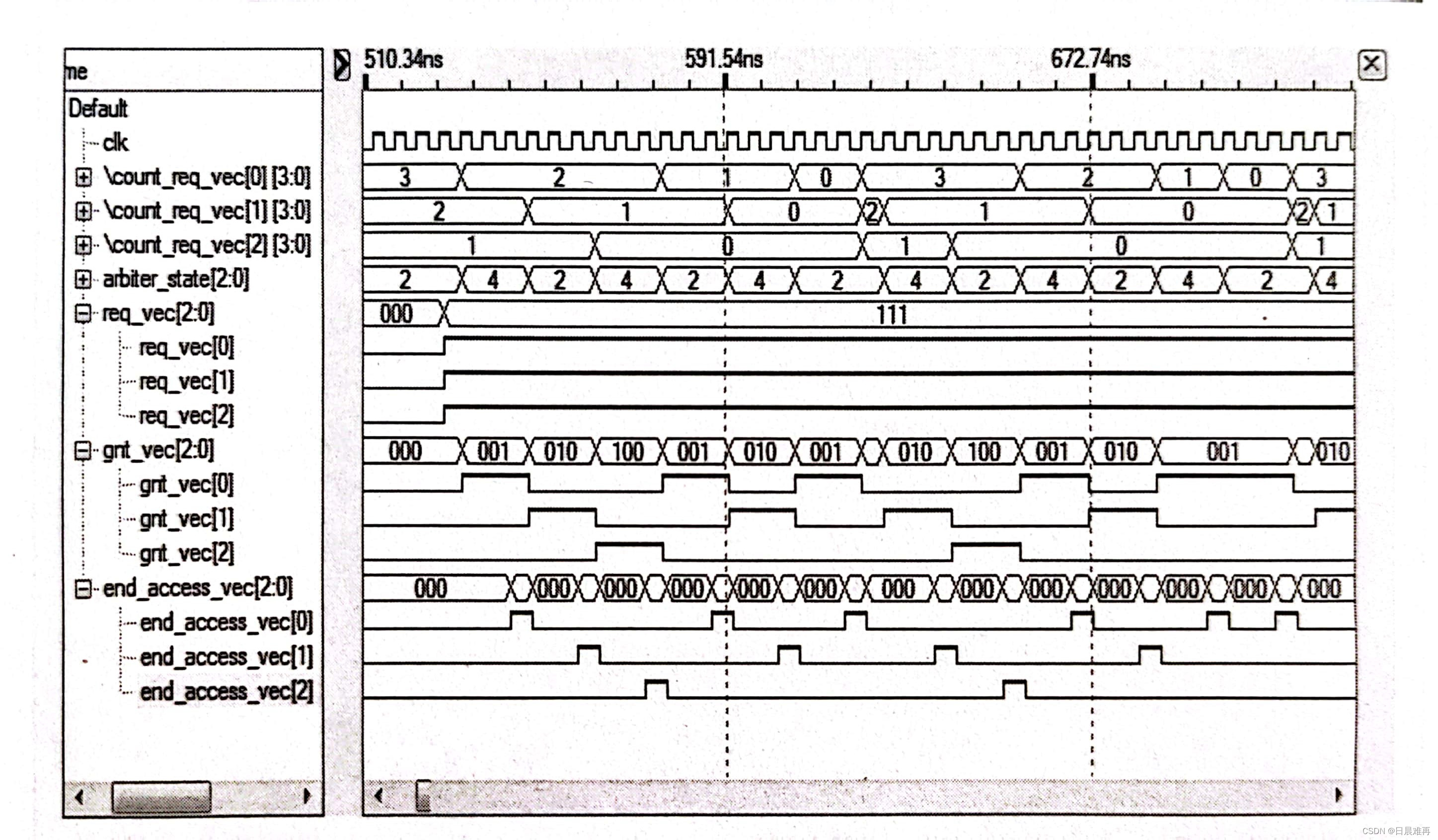

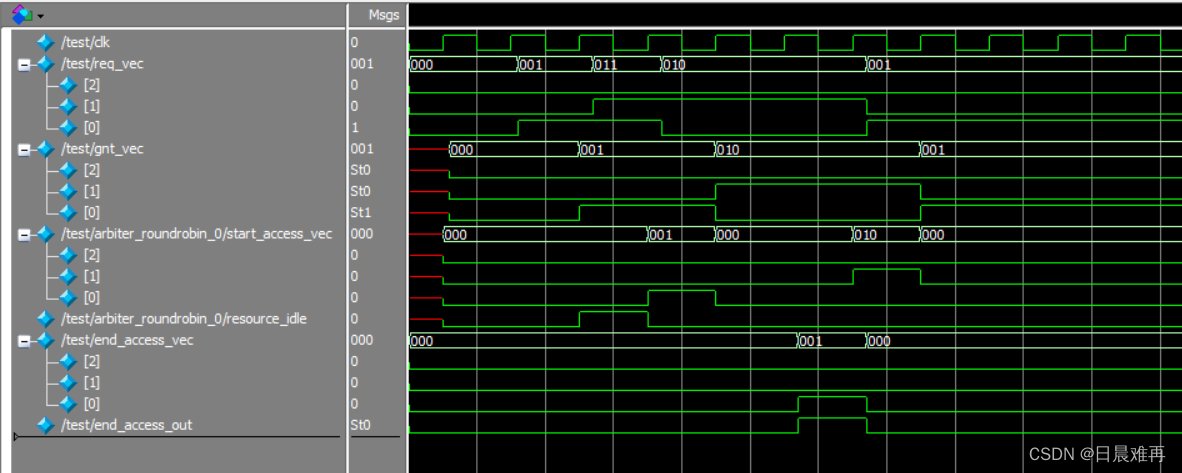

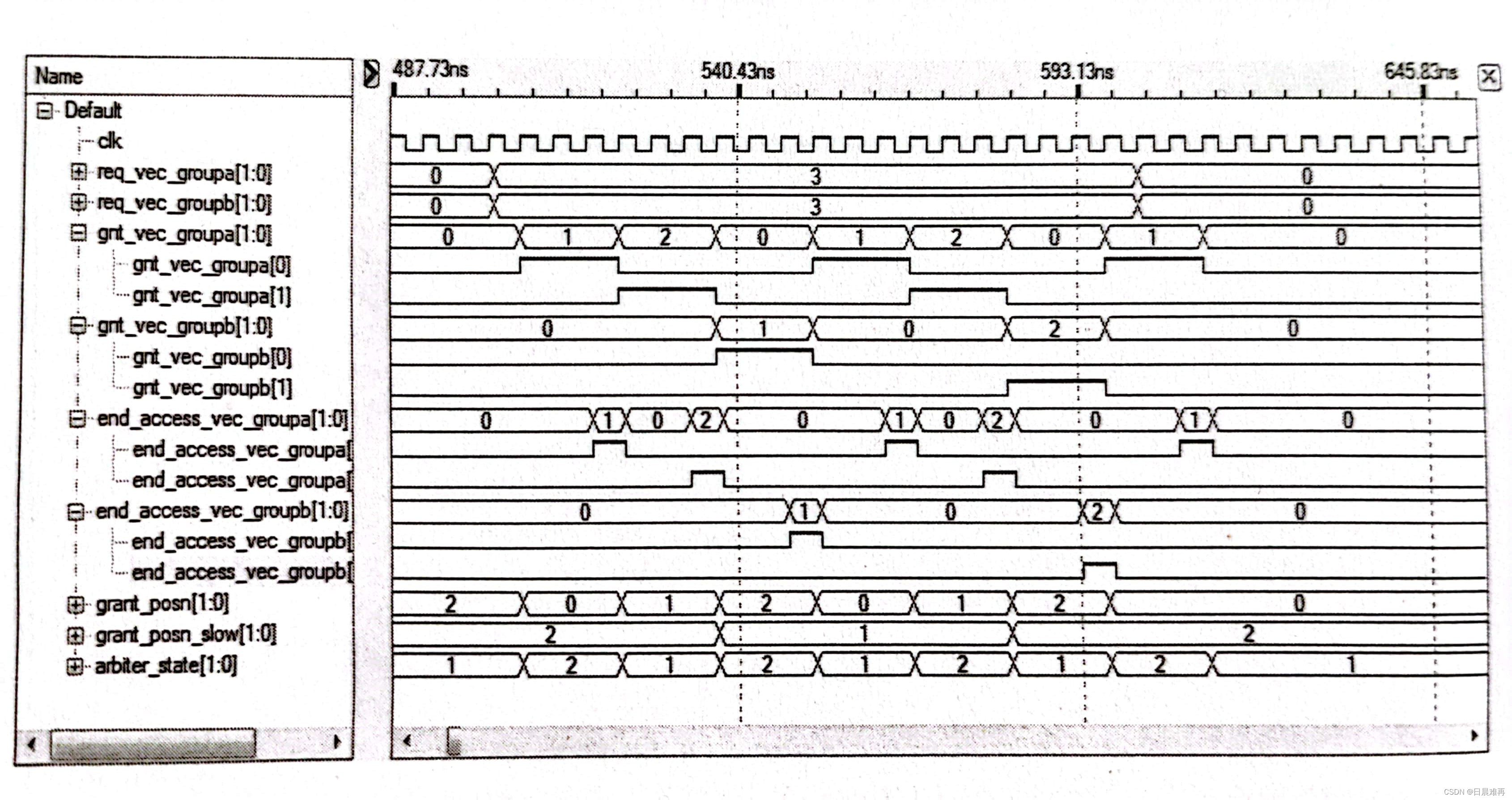

数字IC前端学习笔记:仲裁轮询(三)

相关文章

数字IC前端学习笔记:LSFR(线性反馈移位寄存器)

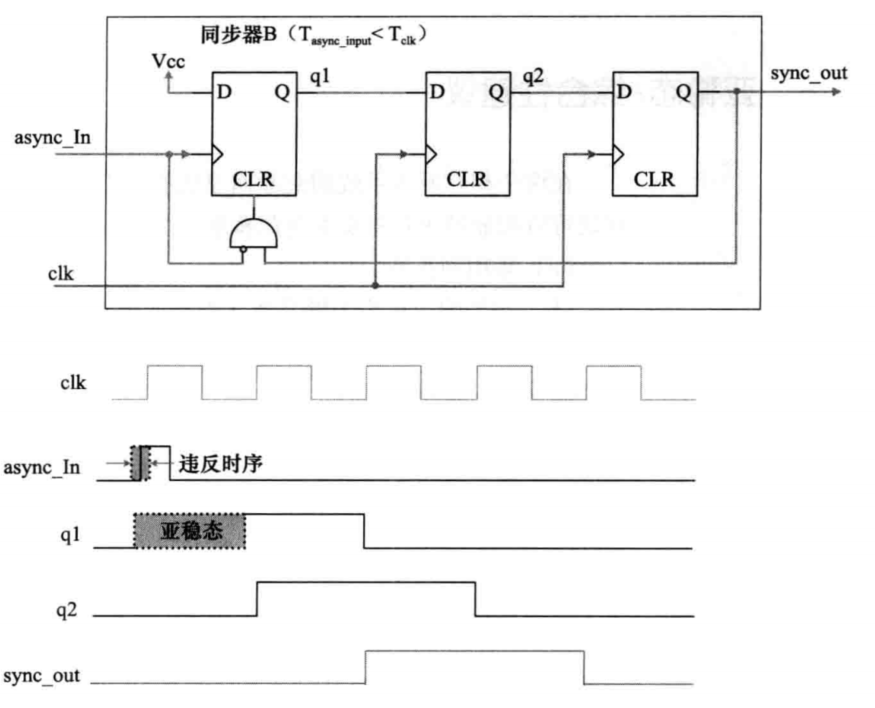

数字IC前端学习笔记:跨时钟域信号同步

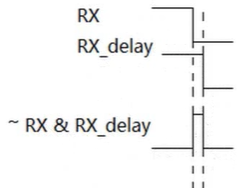

数字IC前端学习笔记:信号同步和边沿检测

数字IC前端学习笔记:锁存器Latch的综合

数字IC前端学习笔记&am…

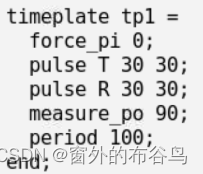

Timeplate Definition

timeplate定义描述单个tester cycle,并指定所有event edges被放置在cycle的位置。

必须在引用之前定义所有的timeplates。一个procedure必须有至少一个timeplate定义,所有的时钟必须在timeplate定义中进行定义,timeplate的定义有以下格式&am…

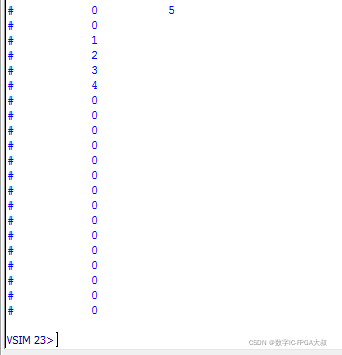

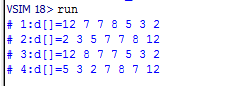

【SystemVerilog】数据类型(2)定宽数组和动态数组

目录

一、定宽数组

1.1定宽数组的声明和初始化

1.2常量数组

1.3数组的基本操作——for、foreach

1.4数组的比较和复制

1.5合并数组

二、动态数组 SV对数组分为两类:定宽数组和动态数组。

定宽数组,一般长度始终固定,且不存在重用性的…

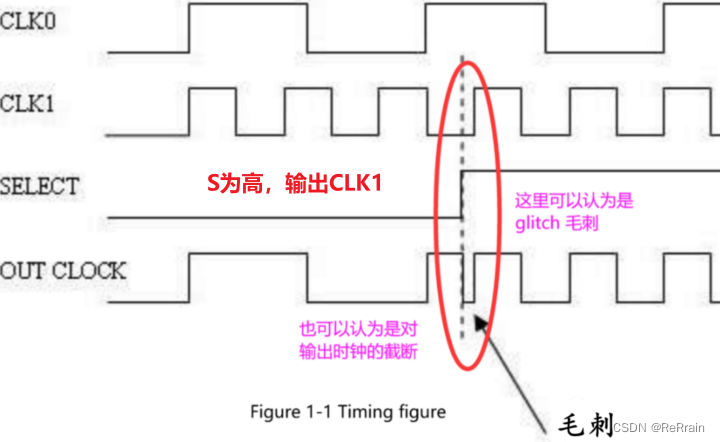

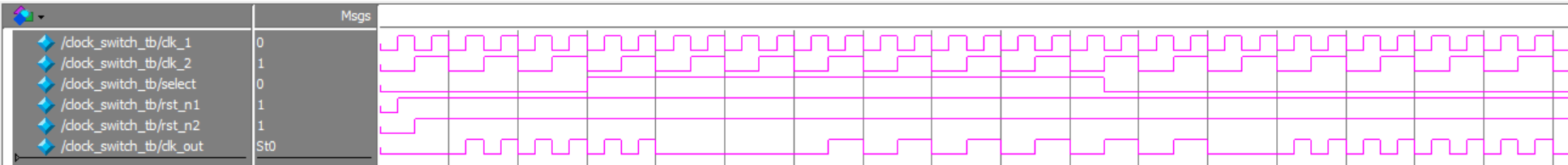

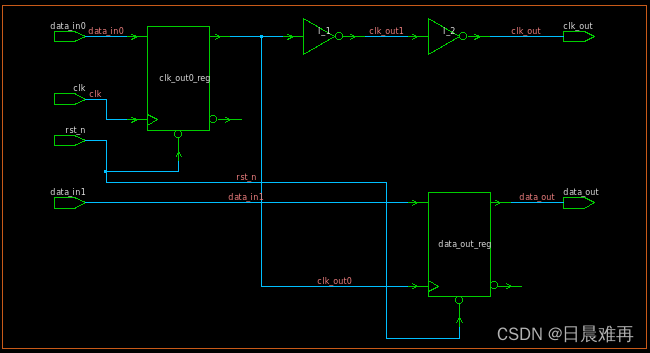

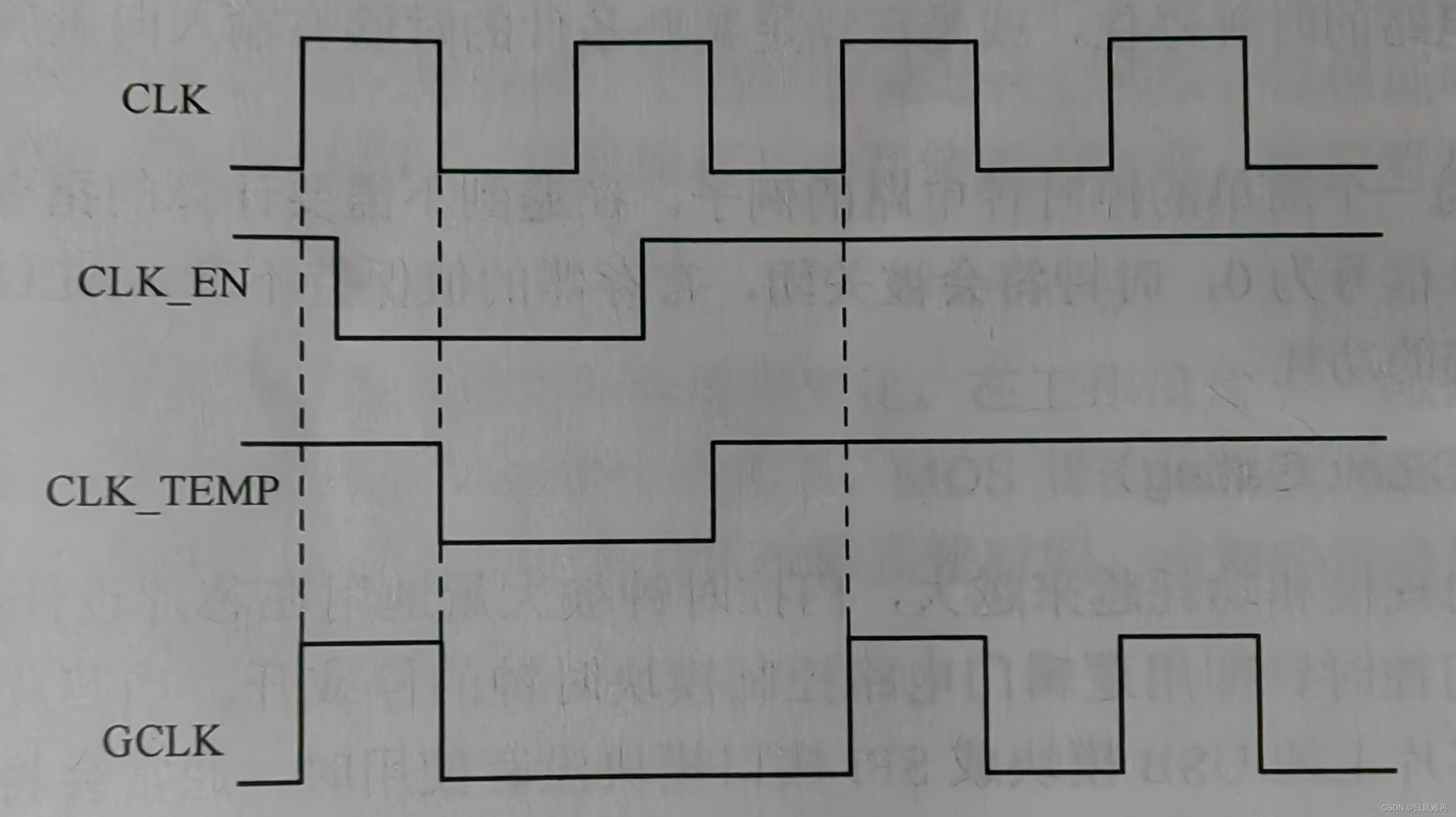

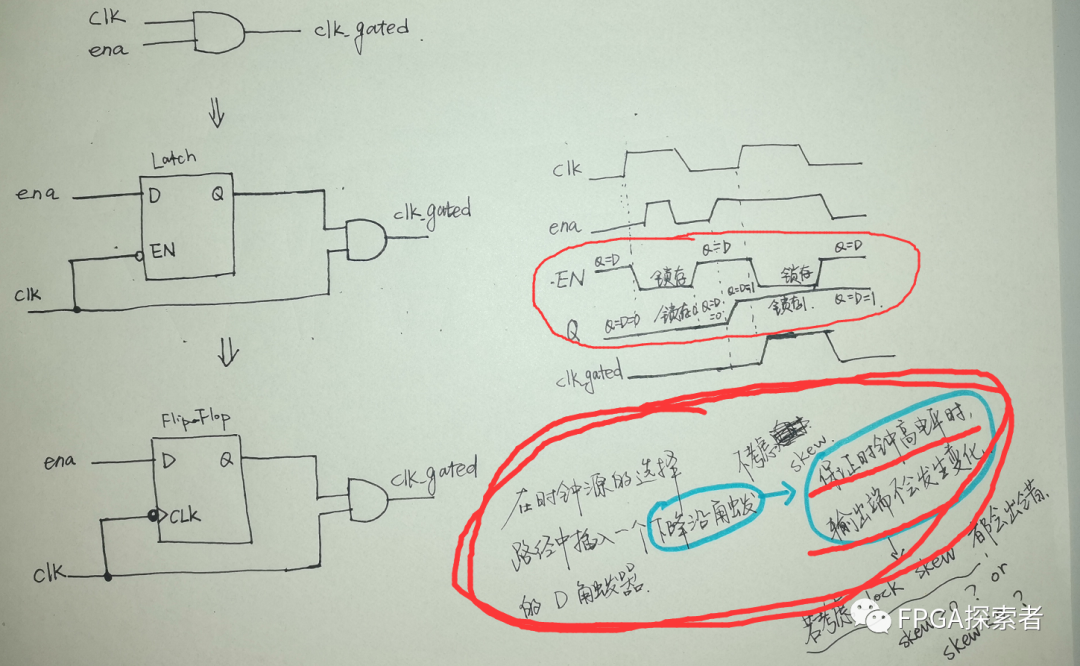

【verilog基础】时钟无毛刺切换电路 Clock Glitch Free

文章目录 一、时钟切换电路:容易产生毛刺二、时钟无毛刺切换电路:在S端增加一些控制通路三、异步时钟无毛刺切换电路:使用同步电路解决亚稳态问题四、真题题目解答一、时钟切换电路:容易产生毛刺 1、在芯片运行时经常需要切换时钟源,通常的实现方式是:通过mux来选择不同的…

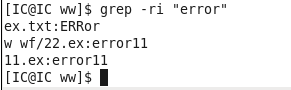

【Linux】数字ICer需要用到哪些Linux命令?

目录

前言

1.目录打开、创建

2.查看

3.对文件的操作

4.查找、定位

5.进程

6.其他 前言 由于IC软件基本都是Linux系统,所以ICer不得不学习Linux系统的操作;但是会用就行,不需要深究。千万别走偏了,纠结看哪本…

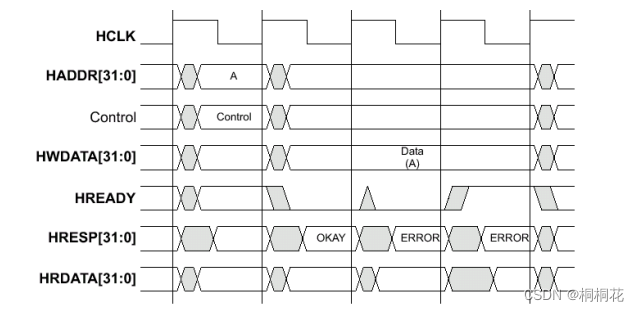

数字ic设计——AMBA总线(2)AHB

典型的AMBA系统:

一个以 AMBA 架构的 SOC,一般来说包含了

AHB(high-performance 的 system bus ): 负责连接例如 ARM 之类的 embedded processor 与 DMA controller,on-chip memory 和其他 interface&…

【verilog基础】用状态机解决交通灯问题

文章目录 一、题目描述:用状态机设计两路交通灯,红灯持续30个clk,绿灯25个clk,黄灯5个clk思路:计数器加状态机二、题目描述:用状态机设计一路交通灯,时钟为1MHz,红灯持续30s,绿灯60s,黄灯5s代码1:分频方法(产生分频时钟)代码2:分频方法(利用倍频方法实现分频器)…

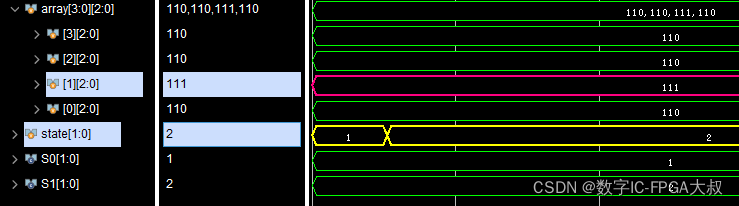

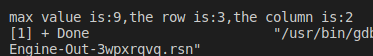

【Verilog】常见bug之for循环

Debug系列文章,想起哪个坑就把它埋了~

本文分享一个for循环的坑,见过了就别再踩了 在Verilog中,我们一般使用for语句进行循环操作。

假设场景: 某项目中,前面代码用到了一个二维数组array[3:0][2:0],如果array[i] 3…

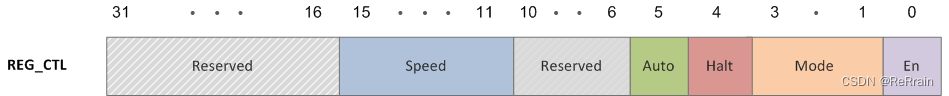

【从零开始学习 UVM】11.1、UVM Register Layer —— Register Layer 概述

文章目录 什么是UVM寄存器层(Register Layer)?寄存器是什么?什么是寄存器块(register block)?什么是内存映射(memory map)?什么是UVM寄存器层(Register Layer)?

UVM寄存器层类用于在待验证设计(DUV)中创建内存映射寄存器(memory-mapped registers)和内存(memo…

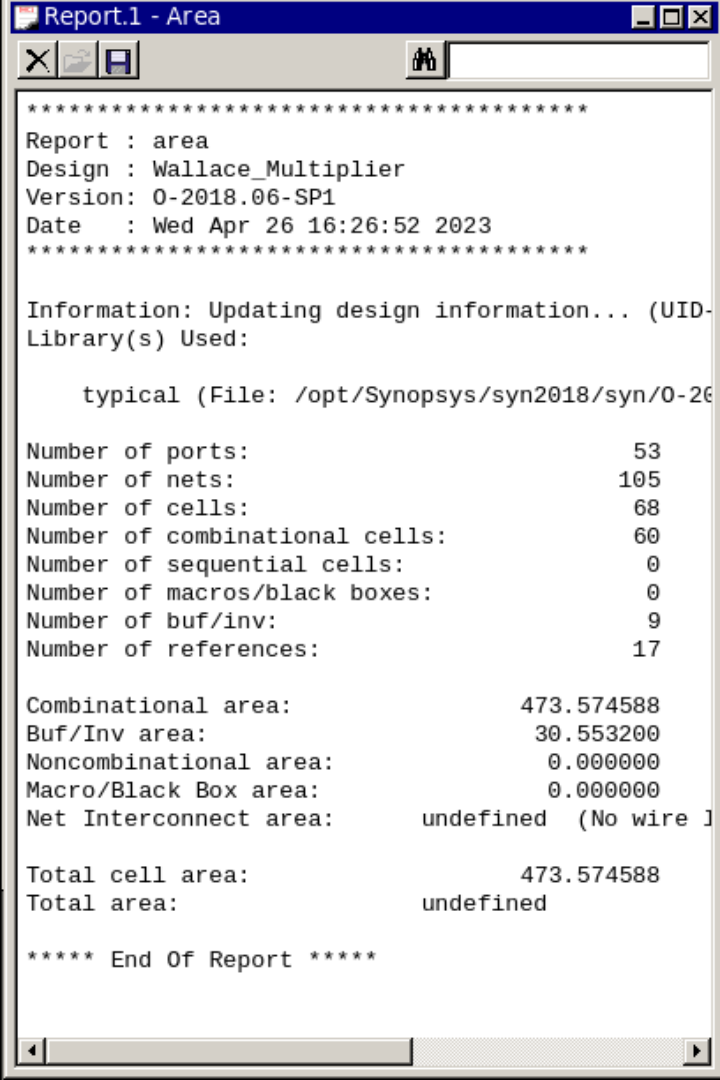

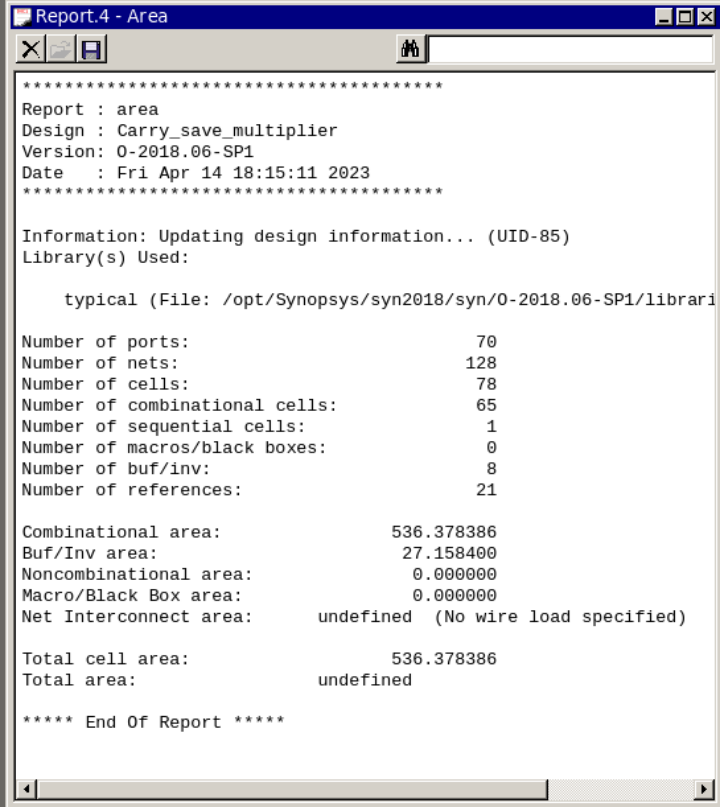

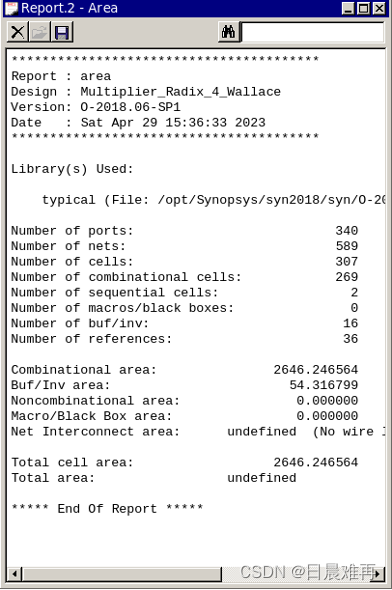

数字IC前端学习笔记:数字乘法器的优化设计(Dadda Tree乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 华莱士树仍然是一种比较规则的结构(这使得可以方便地生成树的结构),这导致了它所使用的全加器和半加器个数不是最少的ÿ…

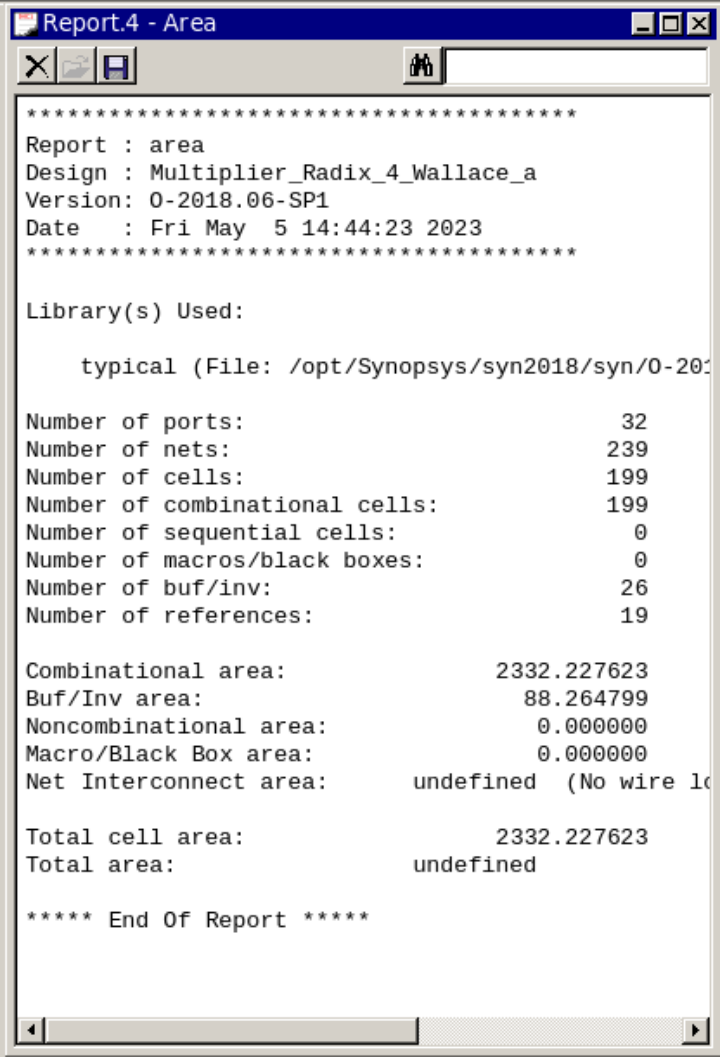

数字IC前端学习笔记:数字乘法器的优化设计(Wallace Tree乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 进位保留乘法器依旧保留着阵列的排列规则,只是进位是沿斜下角,如果能使用树形结构来规划这些进位保留加法器,就能获得更短的关键…

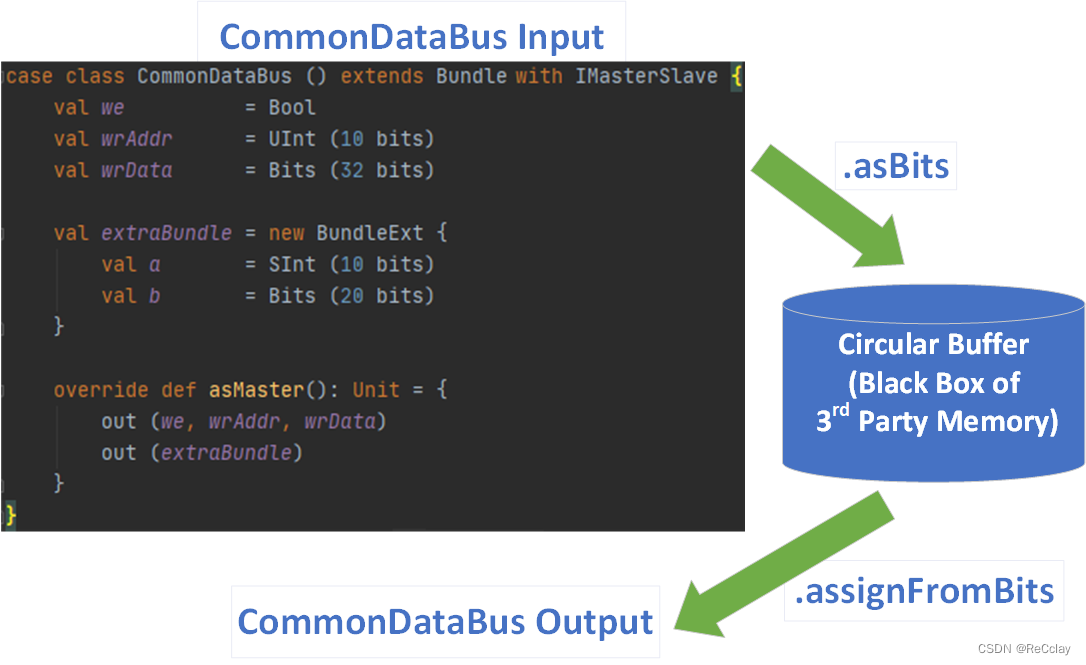

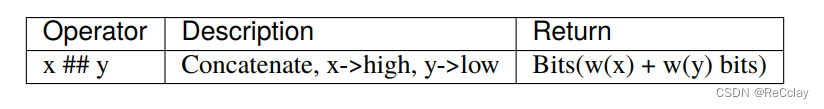

【SpinalHDL快速入门】4.5、复合类型之Bundle

文章目录 1.1、描述1.2、声明1.2.1、条件信号(Conditional signals) 1.3、运算符1.3.1、比较(Comparison)1.3.2、类型转换(Type cast)1.3.3、将比特转换回 Bundle 1.4、IO元素方向1.4.1、in/out1.4.2、mast…

$sformat在仿真中打印文本名的使用

在仿真中,定义队列,使用任务进行函数传递,并传递文件名,传递队列,进行打印 $sformat(filename, “./data_log/%0d_%0d_%0d_0.txt”, f_num, lane_num,dt); 使用此函数可以自定义字符串,在仿真的时候进行文件…

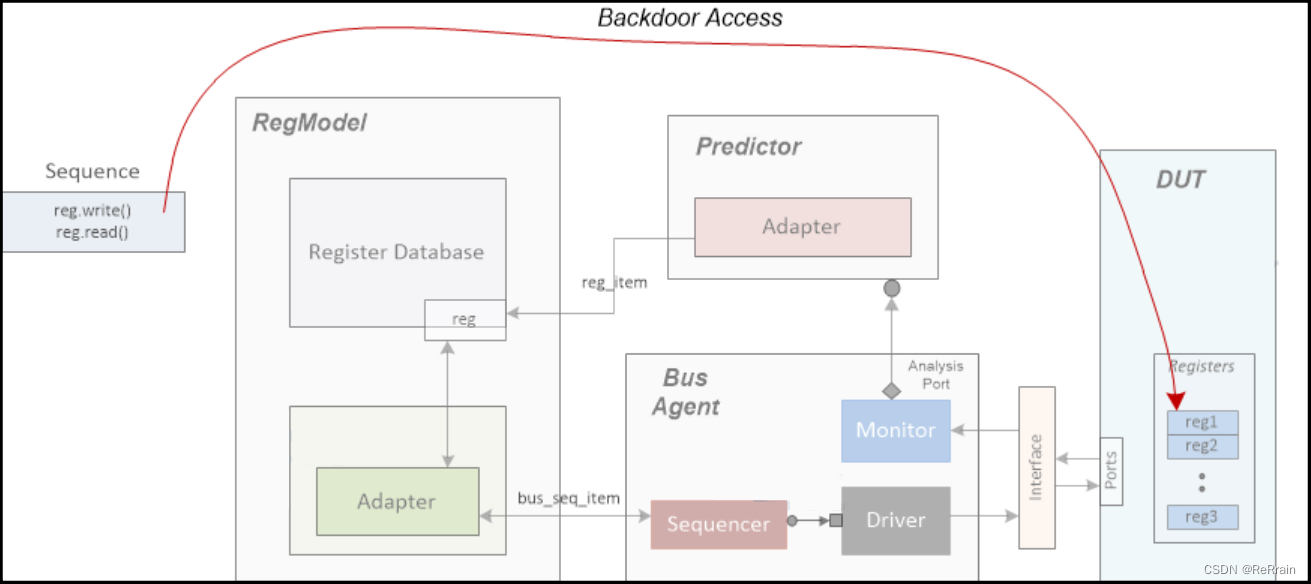

【从零开始学习 UVM】11.3、UVM Register Layer —— UVM Register Environment

文章目录 Register AdapterRegister Predictor创建一个Predictor的步骤1. 声明一个带参数的寄存器预测器版本,与目标总线事务类型一致2. 在注册环境中构建预测器3. 将寄存器映射、适配器和分析端口连接到预测器。Register 环境集成连接寄存器env在上一节寄存器模型(Register …

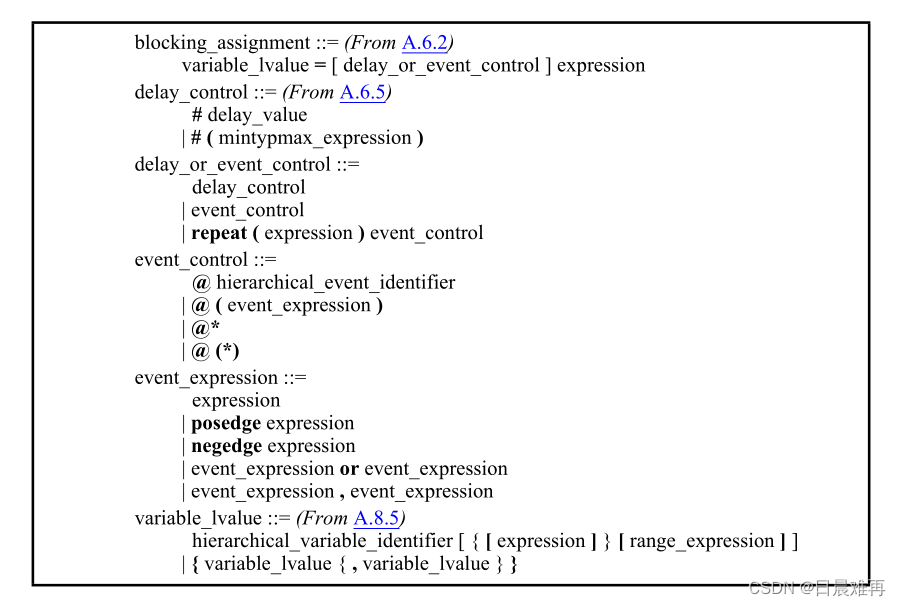

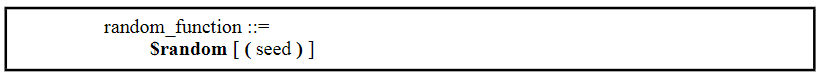

Verilog基础:巴科斯范式(BNF)

相关阅读

Verilog基础专栏https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 由于Verilog HDL标准中对语法的描述使用了Backus Naur Form(BNF)。本文将对其中的约定进行描述。

小写单词,其中一些包含…

7 Series FPGAs GTX/GTH Transceivers

目录 1. Overview2. Block Diagram3. Transmitter4. Receiver5. Physical Coding Sublayer(PCS)6. Physical Medium Attachment(PMA) 本博客为Xilinx 7系列FPGA的千兆比特高速收发器(Gigabit Transceiver, GTÿ…

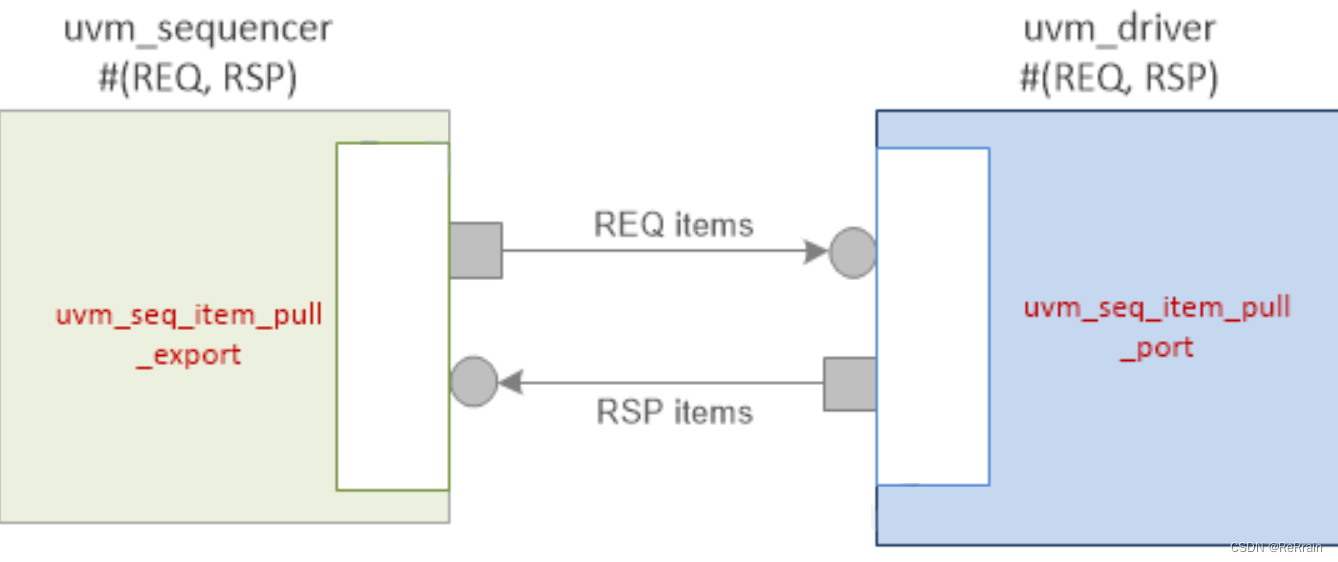

【从零开始学习 UVM】3.5、UVM TestBench架构 —— UVM Sequencer [uvm_sequencer]

文章目录 Usage(用法)Custom Sequencer(自定义sequencer)Class Hierarchy一个 sequencer 生成数据事务作为类对象并将其发送到driver以执行。建议扩展uvm_sequencer基类,因为它包含了允许sequence与driver通信所需的所有功能。基类是由可以被sequencer处理的requset和resp…

数字IC前端学习笔记:数字乘法器的优化设计(华莱士树乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 进位保留乘法器依旧保留着阵列的排列规则,只是进位是沿斜下角,如果能使用树形结构来规划这些进位保留加法器,就能获得更短的关键…

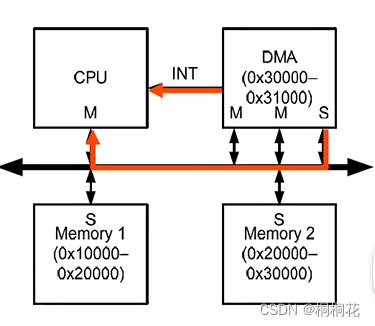

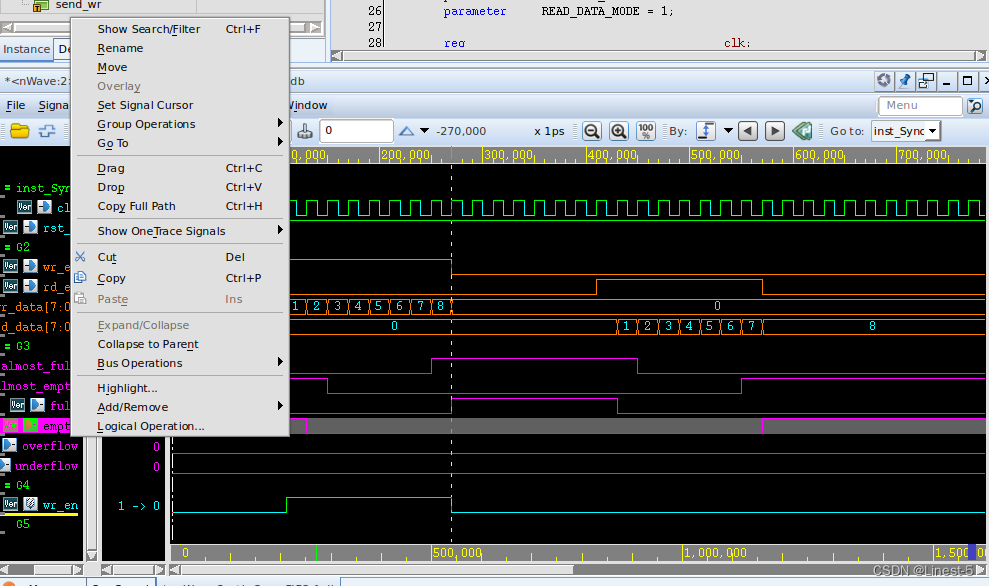

【数字IC基础】同步FIFO(First input Fist output)、异步FIFO、DMA

文章目录 一、FIFO简介二、RAM(Random Access Memory,随机存取存储器)三、同步FIFO四、异步FIFO五、DMA(Direct Memory Access, 直接存储器访问)5、1 DMA的功能5、2 DMA的工作原理一、FIFO简介 1、FIFO 是一种先进先出的数据缓存器,本质上还是RAM;2、在FIFO中存储的数据…

工程师思维是什么?芯片工程师要有哪些思维习惯?

芯片工程师有知识基础和工作技能就够了?

我不同意!

至少这个说法漏掉了很重要的思维,柏拉图说过,“思维是灵魂的自我谈话”。

在IC行业,思维对工程师来说是非常重要的。所以芯片工程师应该具备怎样的核心思维习惯呢…

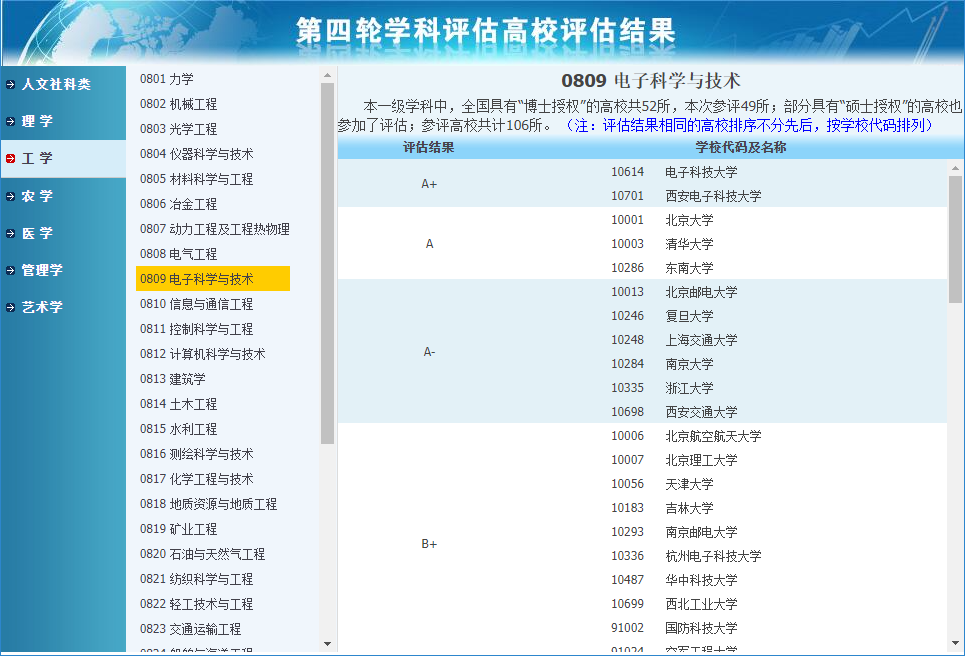

微电子专业 | 哪所大学芯片最强?强在哪?(深度盘点)

今天来聊聊微电子高校,提到微电子专业,肯定不得不说9所首批示范性微电子学院,今天就来盘他们!

类似于专业设置、培养方案、课程设置这类信息,在学校官网上都是可以直接搜索到的,就不和大家赘述了。

这里主…

数字IC前端学习笔记:近期最少使用(LRU)算法

相关文章

数字IC前端学习笔记:LSFR(线性反馈移位寄存器)

数字IC前端学习笔记:跨时钟域信号同步

数字IC前端学习笔记:信号同步和边沿检测

数字IC前端学习笔记:锁存器Latch的综合

数字IC前端学习笔记&am…

【从零开始学习 UVM】9.1、UVM Config DB —— UVM Resource database 资源库详解

文章目录 resource 是一个参数化的容器,可以保存任意数据。资源可用于配置组件、为序列提供数据或在TestBench不同部分之间启用信息共享。它们使用作用域信息(scope)存储,因此其可见性可以限制在TestBench的某些部分中。您可以将任何数据类型放入资源数据库中,并使另一个组…

【SystemVerilog】SV对Verilog的语法改进

SystemVerilog对Verilog兼容,就像C兼容C一样,前者是后者的超集。 目录

一、基本数据类型的改进

1.1SV对表示数字的语法改进

二、SV对设计意图的关键字细化

三、void函数

四、循环语句性能增强

五、隐含的端口连接

六、SV模块的接口 一、基本数据类…

Verilog基础:延时模型

相关阅读

Verilog基础专栏https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 目录

1、连续赋值延时

1.1、赋值内嵌延时

1.2、线网声明延时

1.3、门延迟

2、过程赋值延时

2.1、过程语句前置时序控制

2.2、过程赋值语句内嵌时序控制…

【UVM实战练习项目】2、UVM验证环境基本框架搭建(实例一)(纯软件环境,方便日后测试使用)

本节基于DUT完成UVM验证环境的基本框架搭建,实现对UVM理论知识点进行巩固练习,具体内容包括:如何创建激励、如何建立sequencer、如何连接sequencer和driver,如何集成agent、如何构建env等。 正式开始之前让我们再来回顾下搭建验证环境的过程:首先进行数据建模sequence_ite…

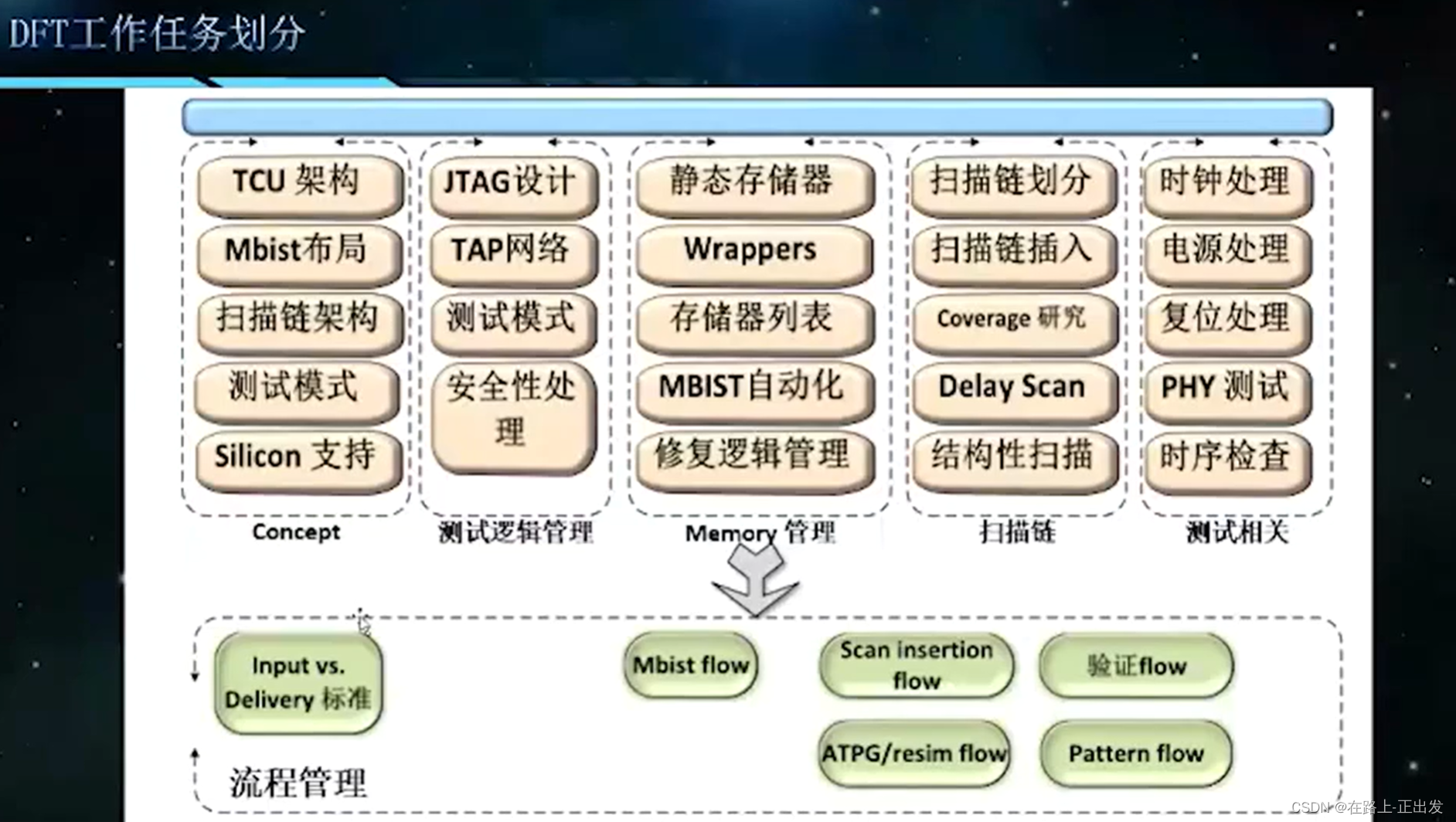

IC流程中 DFT 学习笔记(1)

引言

DFT是ASIC芯片设计流程中不可或缺的环节。其主要目的是在芯片前端设计验证完成后插入一些诸如寄存器链等可供测试的逻辑,算是IC后端设计的范畴。主要是在ASIC芯片流片完成后,通过这些已插入的逻辑,检测流片得到的芯片的制造质量。检测一…

数字IC笔试千题解--编程脚本篇(八)

前言 出笔试题汇总,是为了总结秋招可能遇到的问题,做题不是目的,在做题的过程中发现自己的漏洞,巩固基础才是目的。 所有题目结果和解释由笔者给出,答案主观性较强,若有错误欢迎评论区指出,资料…

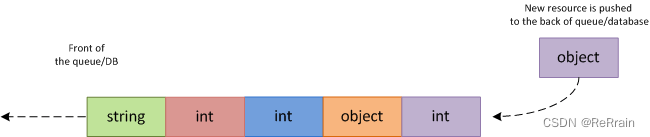

【SystemVerilog】数据类型(4)队列、枚举

本篇文章对SV的其他数据类型进行介绍。包括:链表、队列、枚举、typedef重定义、用户自定义、常量、字符串。 目录

一、队列

二、枚举

三、字符串

四、其他 一、队列 SV 引进了一种新的数据类型——队列,它结合了链表和数组的优点。队列与链表相似&am…

数字ic设计——AMBA总线(1)AMBA总线介绍

AMBA总线介绍 AMBA(Advanced Microcontroller Bus Architecture) 总线是由ARM公司提出的一种开放性的片上总线标准,它独立于处理器和工艺技术,具有高速度低功耗等特点。 总线:系统芯片中各个模块之间需要有接口来连接…

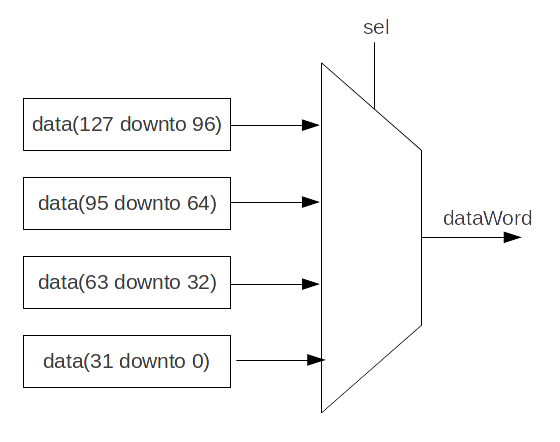

数字电路基础02(用2选1MUX实现与、或、非、与非、或非、异或、同或)

文章目录 2选一MUX用2选一MUX实现与、或、非、与非、或非、异或、同或与门`F=AB`或门`F=A|B`非门`F=A`与非门`F=(A.B)`或非门`F=(A|B)`异或门`F=A^B=AB+BA`同或门`F=A⊙B=A^~B=AB+BA`2选一MUX 当S为1时,A导通(AS);当S为0时,B导通(BS)F=AS+BS(也可根据MUX特点写出真值表,…

【Verilog】testbench仿真对文本数据的读取和写入

在需要进行数据对比的情况下,使用仿真波形来对比查看是比较费劲的,可以将仿真数据写入文本,然后使用文本比较软件(如beyond compare)来进行数据对比验证。 这里介绍一种方式。 实验内容:从文件1(…

笔试题-2023-紫光展锐-数字芯片设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.08.24应聘岗位:数字芯片设计工程师笔试时长:90min笔试平台:nowcoder牛客网题目类型:单选题(18道)、不定项选择题(22道)题目评…

入行IC | 新人入行IC选择哪个岗位更好?

很多同学入行不知道怎么选择岗位。IC的岗位一般有设计、验证、后端、封装、测试、FPGA等等。但是具体到每个人身上,就要在开始的时候确定下你要找的职位,可以有两个或三个,但是要分出主次,主次不分会让你纠结整个找工作的过程。

…

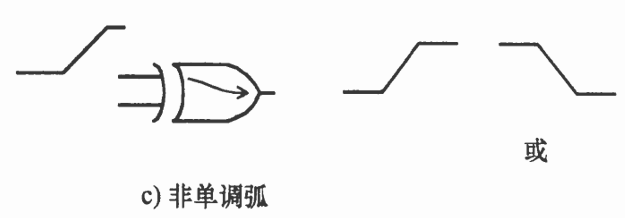

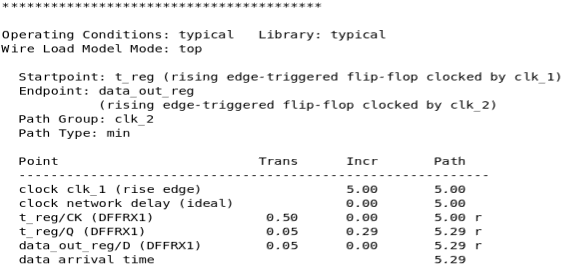

静态时序分析:时序弧以及其时序敏感(单调性)

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm1001.2014.3001.5482 在静态时序分析中,不管是组合逻辑单元(如与门、或门、与非门等)还是时序逻辑(D触发器等)在时序建模时…

数字SOC设计之低功耗设计入门(三)——系统与架构级低功耗设计

前面讲解了使用EDA工具(主要是power compiler)进行功耗分析的流程,这里我们将介绍在数字IC中进行低功耗设计的方法,同时也结合EDA工具(主要是Design Compiler)如何实现。我们的讲解的低功耗设计主要是自顶向…

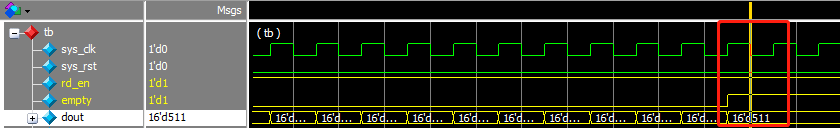

【Verilog】同步FIFO原理及verilog实现(参数化)

旨在学习理解,项目中还是用成熟IP靠谱~ 目录

一、FIFO原理

二、同步FIFO设计

2.1 位宽和深度

2.2 空、满标志

2.3 FIFO计数

2.4 ram模型

2.5 读/写操作

三、verilog代码

四、仿真验证

后记 一、FIFO原理

FIFO( First Input First Output)是…

【Verilog】一文了解verilog基础语法

Verilog很简单,always..if..else走天下。

——鲁迅 目录

前言

一、Verilog HDL简介

二、Verilog模型

三、Verilog模块

四、Verilog数据类型

4.1常量

4.2参数型

4.3变量

4.3.1 wire型

4.3.2 reg型

4.3.3 memory型

五、运算符

六、赋值语句和块语句

6.…

Understanding Lockup Cells

工具会分析扫描链和EDT逻辑之间的控制时序元素的时钟的时序关系,当必须要同步时钟并保持数据完整性时插入边沿触发寄存器(lockup cells)。

可以使用report_edt_lockup_cells命令来展示工具已经插入的lockup cells的详细报告。

Lockup Cell Insertion

工具会分析控制时序元…

Verilog基础:仿真时x信号的产生和x信号对于各运算符的特性

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 信号爆x也许是所有IC人的噩梦,满屏的红色波形常让人头疼不已,但x信号的产生原因却常常只有几种,只要遵循一定的代码规范&#…

笔试题-2023-蔚来-数字芯片设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.08.24应聘岗位:校招-芯片逻辑综合工程师-智能硬件笔试时长:90min笔试平台:nowcoder牛客网题目类型:不定项选择题(15道)、填空题…

Verilog基础:时序调度中的竞争(一)

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序…

【IC】低功耗设计理论知识

一个勤劳的知识搬运工小蜜蜂。 目录

一、功耗的类型

1.1动态功耗 1.2静态功耗

1.3 CMOS工艺的发展与功耗的变化

1.4 SoC中的主要功耗

二、低功耗设计方法 三、低功耗技术

3.1 工艺优化

3.1.1多阈值工艺(Multi-Vt Design)方法 3.1.2电源门控&#…

【EDA Tools】Spyglass 检查 Verilog 和 SystemVerilog 混合语言及 Lint 检查

目录 写在前面

读入设计

发现问题并解决

Lint 检查 写在前面

Spyglass可以用于检查混合设计中的语言互操作性和一致性问题。对于设计中包含多种硬件描述语言的情况,Spyglass 能够识别并解析其中的模块及其互连,并对其进行验证。例如,在包含 Verilog 和 VHDL 的混合设计中…

uvm中transaction的response和id的解读

在公司写代码的时候发现前辈有一段这样的代码:

....//其他transaction

uvm_create(trans);........

uvm_send(trans);

tmp_id trans.get_transaction_id();

get_response(rsp,tmp_id);

如果前面有其他transaction,这段代码里的get_response不带id的话…

Verdi实现信号的平移

在Verilog/System verilog中,# xxx可以实现延迟指定时间的功能,而在使用verdi查看信号波形并进行分析时,同样也可以实现类似的功能。 (注:这种信号平移是有其应用场景的,例如,在某些仿真模型中,…

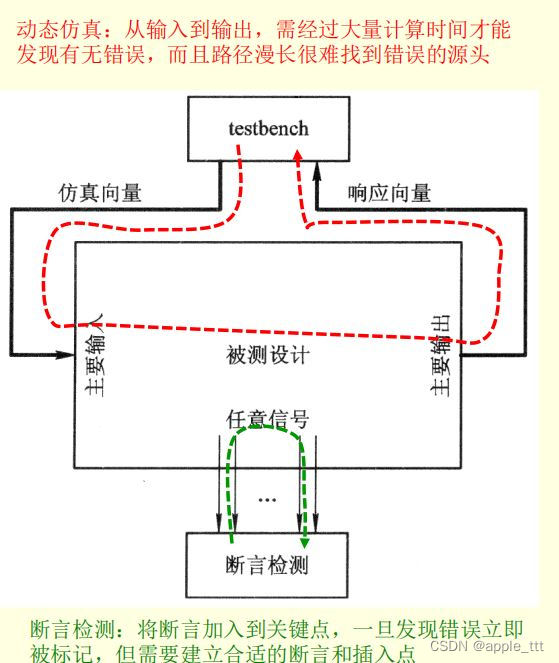

仿真验证方法(1)——动态验证

一、概述

1.1 验证的目的和方法 在现代集成电路设计中,验证所占工作量超过70%。验证要求真实而完备,它决定了设计的成败与成本。 验证的目的 原始描述是否正确?(代码) 逻辑功能是否正确?(功能…

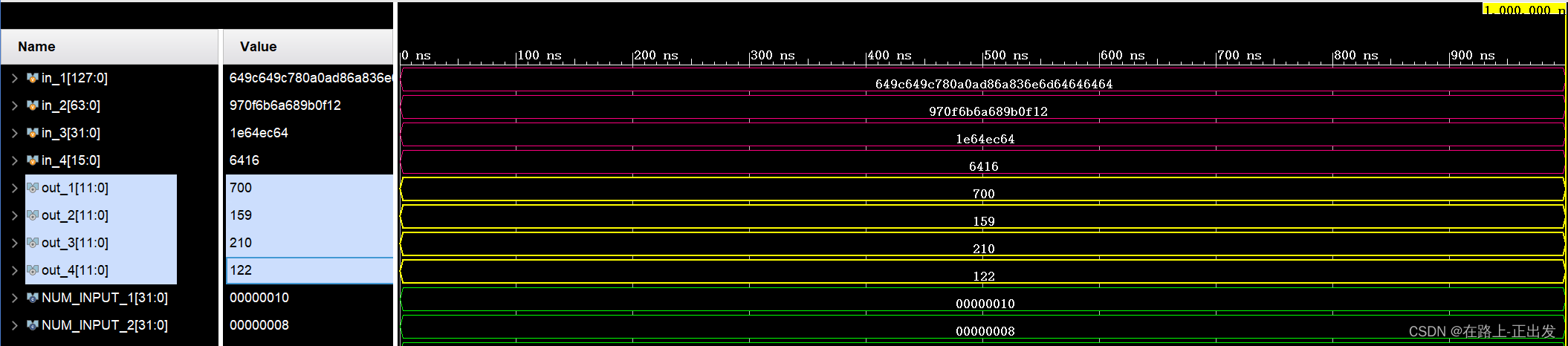

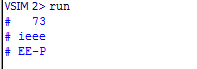

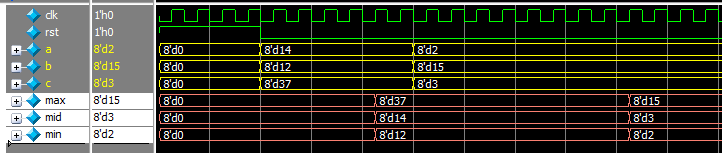

【Verilog】通过任务(task)完成3个8bit数据的冒泡排序

题目:

设计一个模块,通过任务完成3个8位2进制输入数据的冒泡排序。要求:时钟触发任务的执行,每个时钟周期完成一次数据交换的操作。 Verilog代码:

module sort(input sys_clk,input sys_rst,input [7:0] a,in…

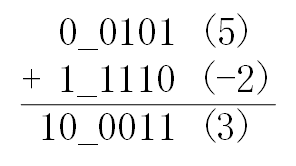

数字IC基础:有符号数和无符号数的加减运算

相关阅读

数字IC基础https://blog.csdn.net/weixin_45791458/category_12365795.html?spm1001.2014.3001.5482 首先说明,本篇文章并不涉及补码运算正确性的证明,仅是对补码运算在有符号数和无符号数中运行进行讨论。 补码运算最大的作用在于消除计算机…

数字IC前端学习笔记:时钟切换电路

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 有些时候我们需要在系统运行时切换系统时钟,最简单的方法就是使用一个MUX(数据选择器)选择输出的时钟,如下代码片所…

微电子专业深度盘点:哪所大学芯片最强?强在哪?(第3弹)

目前国内微电子高校的天花板就是示范性28所微电子学院,我们之前已经讲过了19所,这期视频就来盘点后面这9所高校。 这是微电子高校盘点的第三期,前两期指路:

微电子专业 | 哪所大学芯片最强?强在哪?&#x…

【数字IC基础】FIFO最小深度计算、FIFO深度最好设置成2次幂(可用格雷码编码读写指针)

文章目录 一、FIFO常见参数二、FIFO深度计算2、1 数据突发长度(burst length)2、2 不同场景下的FIFO最小深度计算2、2、1 场景一:写时钟快于读时钟,写和读的过程中没有空闲周期2、2、2 场景二:写时钟快于读时钟,但一次读操作和一次写操作之间间隔两个时钟周期2、2、3 场景…

如何看待OPP给应届生开出40W+的offer?

昨天突然看到一个IC行业的话题上了热榜前三,今天再看更是一度冲到第一。 “如何看待 OPPO 给应届生开出 40w 的待遇?”

再一看还是去年提的问题,突然就被冲上了问答榜单,我怀疑是绿厂自己动的手,但我没有证据。 不过还…

【数字IC第一步】Linux系统安装(含常用IC软件)

为了简易入手,本虚拟机系统集成了主流IC软件。

资源来自网络,也当共享于网络。

链接:https://pan.baidu.com/s/1Oh-CTBuorHDkQkfGhmm_Wg 提取码:1csc 目录

前言

一、VMware安装

二、VMware运行 三、软件介绍 后记 前言…

学员追访丨双非硕士大厂逆袭

数字验证二期-李同学:陕科大软件工程硕士

offer:北京奕*伟(西安分部)-17K14

毕业后的现实

我是属于典型的双非院校的硕士,本科读的专业是电气工程及其自动化专业,硕士阶段主要跟导师做FPGA。

从去年的…

一篇文章带你认识芯片分类及代表企业

芯片的分类方式可以有很多种,如果我们随机采访10位业内大佬,也许会得到10种不同的答案。 举个例子,按照处理信号方式可分为模拟芯片和数字芯片。 按照设计理念可分为可分为通用芯片和专用芯片。 按照应用领域可分为航天级芯片,汽车…

Tcl语言:SDC约束命令create_generated_clock详解(上)

相关阅读

Tcl语言https://blog.csdn.net/weixin_45791458/category_12488978.html?spm1001.2014.3001.5482 有时候,复杂的设计需要多个时钟来完成相应的操作,当设计中有多个时钟存在时,它们需要相互协作或各司其职。有几种时钟可能由其他时…

数字IC前端学习笔记:仲裁轮询(六)

相关文章

数字IC前端学习笔记:LSFR(线性反馈移位寄存器)

数字IC前端学习笔记:跨时钟域信号同步

数字IC前端学习笔记:信号同步和边沿检测

数字IC前端学习笔记:锁存器Latch的综合

数字IC前端学习笔记&am…

【从零开始学习 UVM】3.7、UVM TestBench架构 —— UVM Monitor [uvm_monitor]

文章目录 什么是 monitor ?UVM monitor是做什么的?创建UVM monitor的步骤什么是 monitor ?

一个 UVM monitor 负责从设计接口捕获信号活动,并将其转换为可发送到其他组件的事务级数据对象。为了做到这一点,它需要以下内容: 虚拟接口句柄来处理此monitor尝试监视的实际接…

数字IC前端学习笔记:优化的基4布斯编码华莱士树乘法器

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html 本文是对前文设计的乘法器,即基4布斯编码华莱士树乘法器的补充和优化,具体关于基4布斯编码和华莱士树的内容可以从以往的文章中获得。

数字IC前端学习笔记ÿ…

【SystemVerilog基础】面向对象编程(OOP,Object Oriendted Programming)

文章目录 一、为什么要使用面向对象编程的方法?二、OOP(Object Oriendted Programming)相关概念三、类CLASS3、1、类的基本概念3、2、类的构造函数`new()`3、3、静态变量(被这个类的所有实例(对象)共享)和全局变量(整个测试平台均可访问)3、4、类的示例代码:用类验证数…

数字IC基础:有符号数和无符号数加、减法的Verilog设计

相关阅读

数字IC基础https://blog.csdn.net/weixin_45791458/category_12365795.html?spm1001.2014.3001.5482 本文是对数字IC基础:有符号数和无符号数的加减运算一文中的谈到的有符号数加减法的算法进行Verilog实现,有关算法细节请阅读原文࿰…

秋招已至,来看看数字IC设计岗位的招聘标准

秋招将至,不对,秋招已至。

关注秋招的同学应该已经发觉了——今年的秋招提前了。

大厂官网的校招信息在逐步更新,招聘海报在高校的IC社群里开始冒头,隔三差五还会有HR给你打电话。

无论是微电子科班的同学,还是其他…

从事IC工作,IC公司招人都看重哪些方面?

比起去年拿着40W招不到应届生的局面,今年IC企业在招聘方面似乎更偏向“理性”了一些。 但在当前的市场环境下,依然还是人才供不应求。 当求职者们还在内心OS“求职难”的时候,招聘者也在深受“招聘难”的困扰。 也就是说,岗位机会…

芯片科普 | IC新人入行如何选择岗位?

IC行业的产业环节众多且环环相扣,每个环节都需要不同职责的工程师。这篇文章主要以IC设计环节的岗位为主,帮大家提供择岗的思路。

建议先了解行业

从个人求职的角度出发,建议先了解一些概况,是为了确定自己是否适合这个行业&…

数字设计小思 - D触发器与死缠烂打的亚稳态

前言

本系列整理数字系统设计的相关知识体系架构,为了方便后续自己查阅与求职准备。在FPGA和ASIC设计中,D触发器是最常用的器件,也可以说是时序逻辑的核心,本文根据个人的思考历程结合相关书籍内容和网上文章,聊一聊D…

【从零开始学习 UVM】2.6、UVM 基础功能 —— UVM Object Pack/Unpack

UVM自动化宏还包括将类变量打包(pack)成位或字节流的机制,以及解包(unpack)缩位流并填充类内容。在处理SPI、I2C和RS-232等串行通信形式时,这特别有用。 文章目录三种 pack/unpack 方法介绍使用自动化宏pac…

【从零开始学习 UVM】10.5、UVM TLM —— UVM TLM Blocking Get Port

文章目录 UVM TLM Get Port Example1. 创建一个发送方类,其端口类型为 uvm_blocking_get_imp3. 创建接收器类,等待 get 方法。4. 在更高层次上连接端口及其实现Get端口阻塞行为任何组件都可以通过 TLM get 端口请求从另一个组件接收事务。发送组件应定义获取端口的实现。该实…

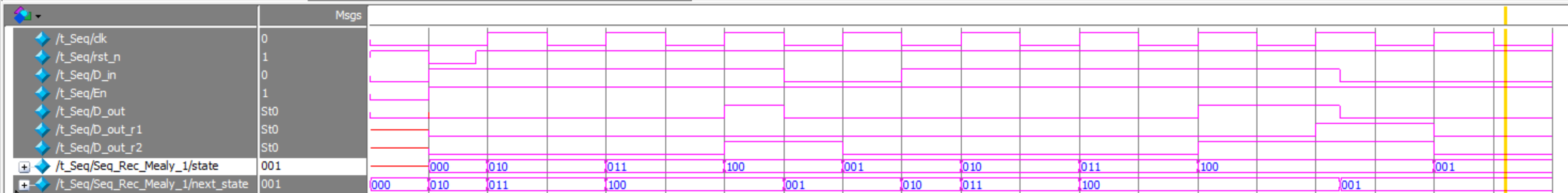

Verilog基础:三段式状态机与输出寄存

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html 对于Verilog HDL而言,有限状态机(FSM)是一种重要而强大的模块,常见的有限状态机书写方式可以分为一段式,二段式和三段式,笔者强烈建议使用三…

【SpinalHDL快速入门】6.2、SpinalHDL语法之When/Switch/Mux

文章目录 1.1、When1.2、Switch1.2.1、实例1.2.2、附加选项 1.3、本地声明1.4、Mux1.5、位选择1.5.1、实例 1.1、When

与VHDL和Verilog一样,当满足指定条件时可以对信号进行有条件的赋值:

when(cond1) {// Execute when cond1 is true

}.elsewhen(cond…

【计算机组成原理】Cache缓存:高速缓冲存储器

文章目录 一、为啥要有Cache?1、1、计算机的存储结构(memory hierarchy)1、2、为什么需要Cache?1、3、L1\L2\L3Cache?二、程序访问的`局部性locality`:==时间局部性、空间局部性==2、1、时间局部性:同一份数据在短时间内往往会被多次重复使用2、2、空间局部性:临近的数…

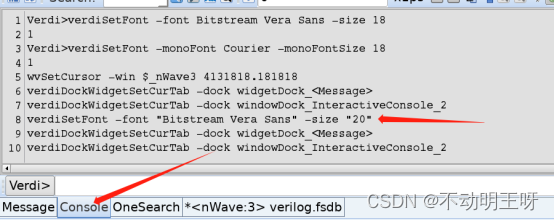

verdi如何打开时可以加载配置比如字体

打开tcl使能 找到配置字体的命令 其实其他有需要的文件配置都可以在这里找到对应的指令

存储文件 新建verdi001.tcl文件 输入想要调整的字体以及大小

verdiSetFont -font "Bitstream Vera Sans" -size "18"

verdiSetFont -monoFont "Courier&q…

静态时序分析:SDC约束命令set_case_analysis详解

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm1001.2014.3001.5482 目录

指定值

指定端口/引脚列表

简单使用 set_case_analysis命令用于对电路进行特定模式的设定,例如对于一个工作在正常模式下的芯片,…

笔试题-2023-加特兰-数字IC设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.07.27应聘岗位:数字电路设计工程师(SoC) - 2023届笔试时长:90min笔试平台:nowcoder牛客网题目类型:问答题(11道)主观评价 难易…

静态时序分析:静态时序分析的原理及其两种模式PBA、GBA

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm1001.2014.3001.5482 静态时序分析有两种模式:PBA(Path Based Analysis)和GBA(Graph Based Analysis),PBA是基于路径的分析模式而GBA则是基于图的分析模式。在…

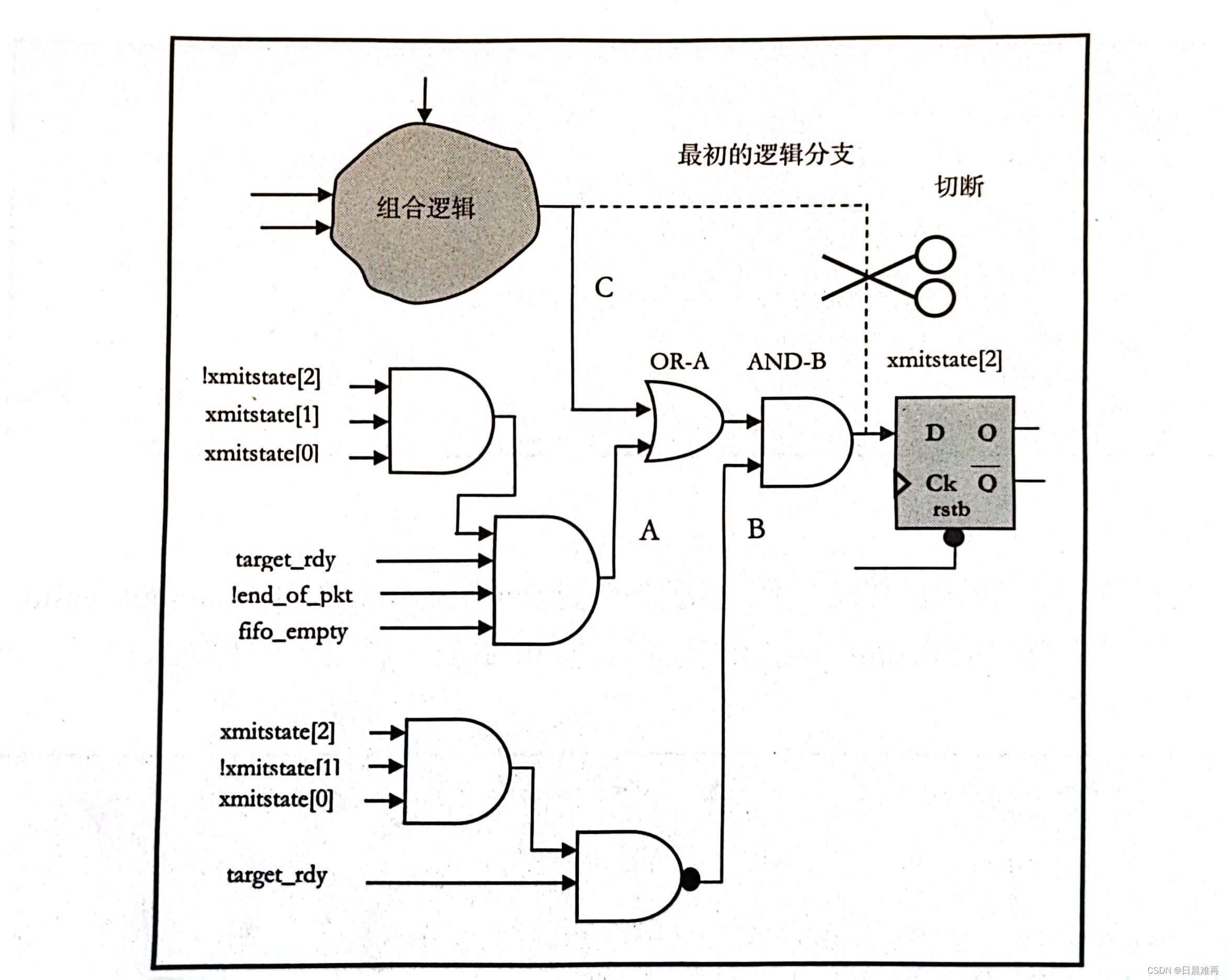

数字IC后端学习笔记:等效性检查和ECO

1.形式验证工具 对于某些电路的移植,一般不需要对新电路进行仿真验证,而可以直接通过EDA工具来分析该电路的功能是否与原电路一致,此种验证方法可以大量减少验证时间,提高电路的效率。 等效性检查(Equivalence Check&a…

【从零开始学习 UVM】12.8、UVM RAL(续更) —— UVM RAL Model 实战项目(基于AXI总线的寄存器读写实例)

让我们了解寄存器模型是如何构建的,将其与验证环境集成,并使用读写方法访问DUT寄存器。 文章目录 1.1 R寄存器描述1.2 Testbench Block 图1.3 Testbench hierarchy1.4 总体步骤1.4.1 步骤1:创建注册(RAL)模型的步骤1.4.1.1 Step A: 编写寄存器类1.4.1.2 Step B: 编写寄存器…

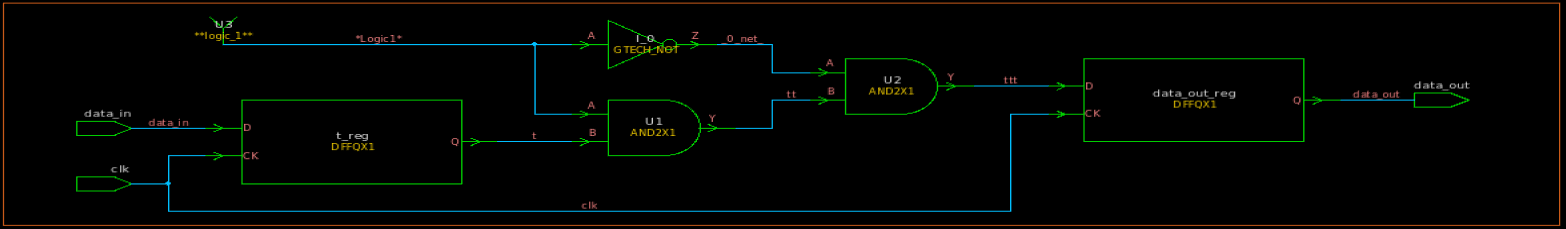

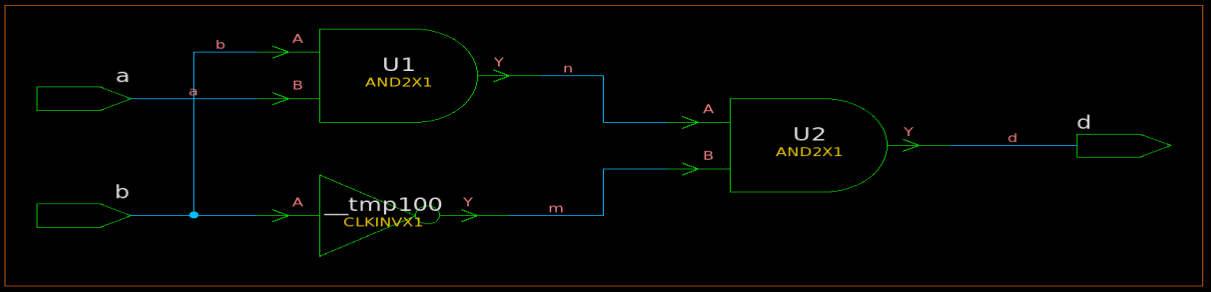

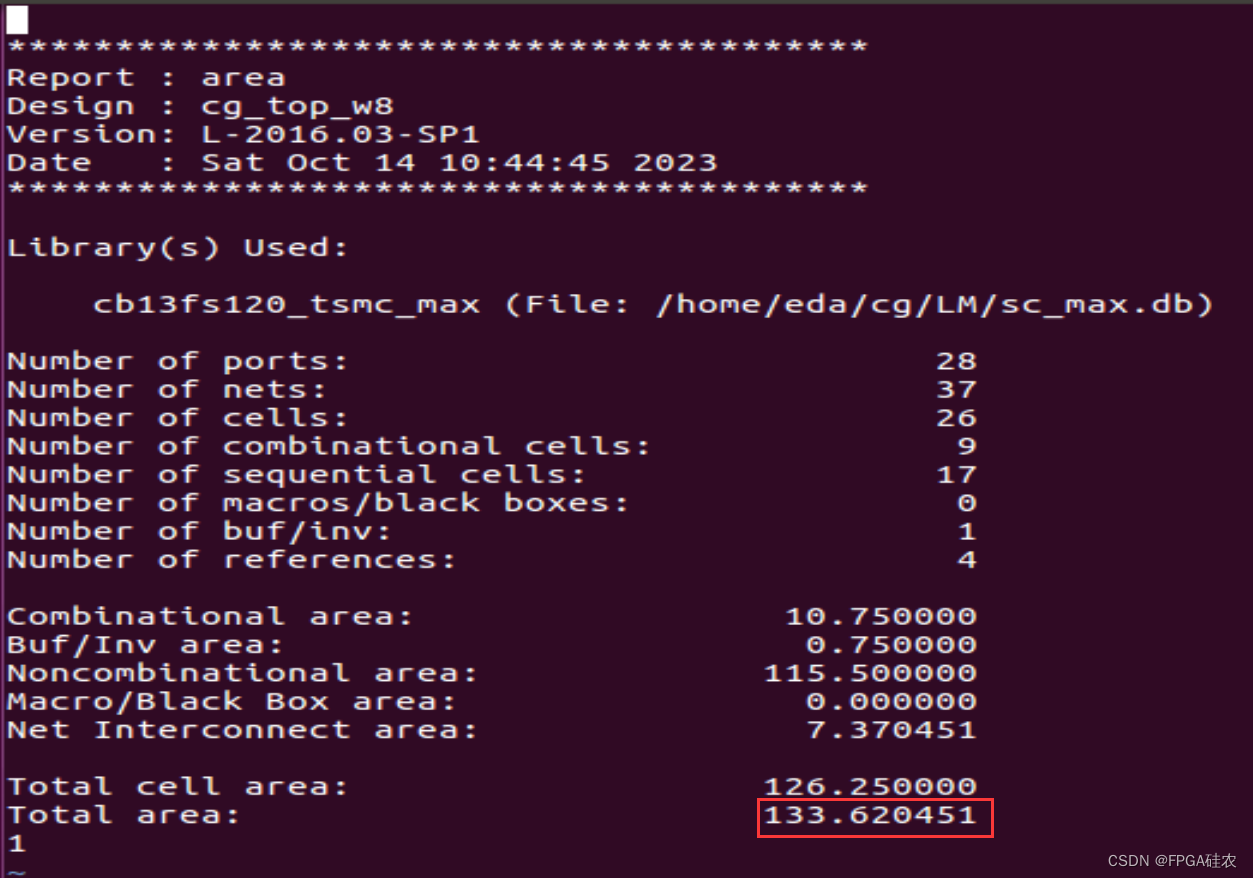

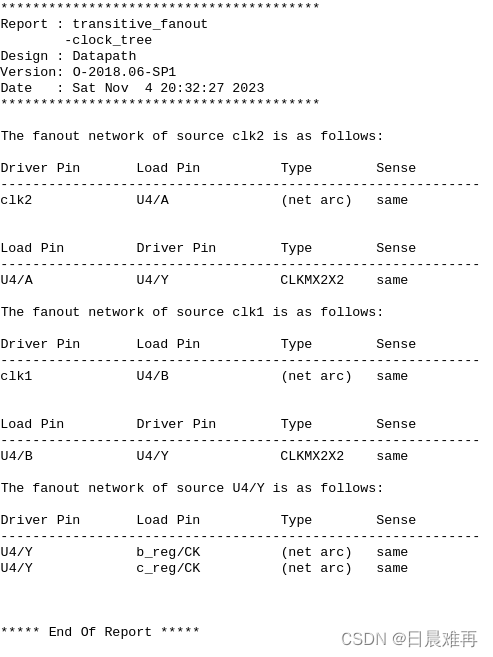

【数字IC设计】DC自动添加门控时钟

简介

数字电路的动态功耗主要是由于寄存器翻转带来的,为了降低芯片内部功耗,门控时钟的方案应运而生。作为低功耗设计的一种方法,门控时钟是指在数据无效时将寄存器的时钟关闭,以此来降低动态功耗。

在下图中,展示了…

Tcl语言:SDC约束命令create_generated_clock详解(下)

相关阅读

Tcl语言https://blog.csdn.net/weixin_45791458/category_12488978.html?spm1001.2014.3001.5482 设定生成时钟特性 前文的末尾提到,当使用-divide by或-multiply_by选项创建生成时钟时,会根据master clock的时钟周期派生出生成时钟的周期&am…

DFT和ATE岗位前景薪资对比,手把手教你如何选择岗位?

ATE测试和DFT可测性设计,虽然二者都对芯片测试至关重要,但是两个岗位的区别还是很大的。

两个岗位应该如何做选择? 先讲产业环节

我们知道芯片设计、芯片制造、芯片封测每个环节都是大工程,且每个环节都关键且重要。测试是芯片诞…

静态时序分析:SDC约束命令set_clock_transition详解

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm1001.2014.3001.5482 在静态时序分析:SDC约束命令create_clock详解一文的最后,我们谈到了针对理想(ideal)时钟,可以使用set_clock_transition命令直…

【数字IC设计】Verilog计算x/255的商和余数

问题描述

已知x是16位无符号整数,求x除以255的余数和商。尽量降低实现方式的硬件开销(包括面积和时序)

思路

由于除数255是一个常数,因此,直观上给人的感觉就是应该有相应的优化方法,即相对于除数可变的实现方式,在面积、时序方面应该有所改善。 对于该问题,本文给出…

FPGA基础:Verilog HDL

文章目录 一、Verilog HDL简介二、Verilog语法2.1 逻辑值2.2 变量属性2.3 变量类型(`wire、reg`)2.4 参数(`parameter 、localparam` )2.5 常量(`b、0、d、h`)2.6 赋值语句(`<=、=`)2.7 关系运算符2.8 算术运算符2.9 归约运算符(`结果为1bit`)、按位运算符(`n位则结果为n…

centos版本的EDA虚拟机搭建3

0、参考博客

1、CentOS 7 下 rar unrar的安装

1、配置虚拟机与主机共享文件夹。 **前提,虚拟机关机。**之后进行虚拟机设置,选项-共享文件夹,点击总是启用,之后添加共享文件夹名称。 之后打开虚拟机,命令行输入v…

数字IC前端学习笔记:数字乘法器的优化设计(进位保留乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 阵列乘法器设计中限制乘法器速度的是随着数据位宽而迅速增大的串行进位链,如果使用进位保留加法器,则可以避免在设计中引入较长时间的等待&…

数字IC前端学习笔记:门控时钟

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 门控时钟(clock gating)技术作为一种传统的动态低功耗技术被广泛应用于现在的数字集成电路设计中,这是RTL级别的低功耗优化技术。门控时钟即使用逻辑门…

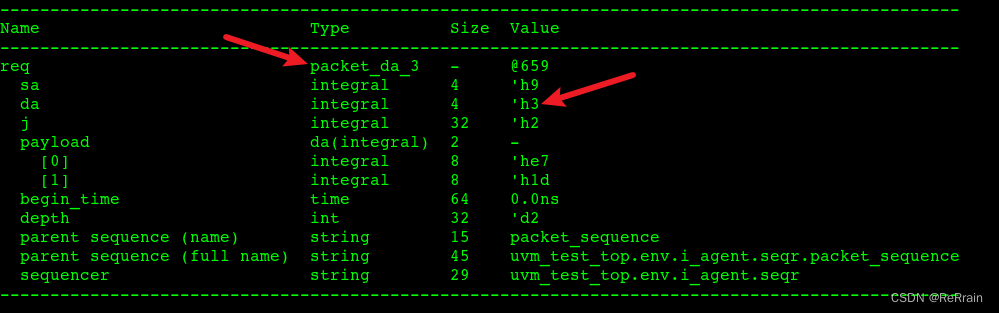

【从零开始学习 UVM】8.2、Reporting Infrastructure —— uvm_printer 详解

文章目录 老派风格在UVM中如何完成uvm 风格Table printerTree printerLine printerprint使用print使用条件使用konb更改print配置示例在一个随机验证环境中,数据对象不断地由不同的组件生成和操作,如果能够显示对象的内容,则调试会变得更加容易。

老派风格

传统上,这是通…

【从零开始学习 UVM】3.8、UVM TestBench架构 —— UVM Agent [uvm_agent]

文章目录 什么是 UVM Agent?所有的Agent Type是什么?如何确定UVM Agent是主动还是被动的?创建UVM代理的步骤一个UVM代理做什么?如何将UVM代理配置为主动或被动?一个UVM Agent例子推荐做法什么是 UVM Agent?

一个 Agent 将Sequencer、Driver和Monitor封装成一个单一实体,…

Tcl语言:SDC约束命令create_clock详解

相关阅读

Tcl语言https://blog.csdn.net/weixin_45791458/category_12488978.html?spm1001.2014.3001.5482 在一个设计中创建一个时钟对象的SDC命令是create_clock。该指令的BNF范式(有关BNF范式,可以参考以往文章)为:

create_…

【数字IC基础】IR DROP学习总结(含笔试真题实战)

文章目录 理论基础IR DROP概念IR DROP分类静态IR DROP动态IR DROP改善IR DROP的方法真题真题1真题2真题3真题4参考理论基础

IR压降是指出现在集成电路中电源和地网络上电压下降或升高的一种现象。随着半导体工艺的演进,金属互连线的宽度越来越窄,导致它的电阻值上升,所以在…

【SpinalHDL快速入门】三、Scala 快速入门

SpinalHDL本质上来讲是Scala语言的一个库,所以需要先学习Scala,才能在此基础上学习SpinalHDL。 文章目录 Scala 基础Scala 数据类型(5种:Boolean、Int、Float、Double、String)Scala VariablesScala FunctionsReturnRe…

静态时序分析:SDC约束命令set_drive详解

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html 本章将讨论使用set_drive命令,它用于对输入端口的驱动能力建模。首先需要说明的是,默认情况下,DC在STA时默认输入端口的转换时间是0,这对于…

数字IC笔试题——门控时钟与控制信号电平、与门门控、或门门控、上升沿门控、下降沿门控

门控时钟问题。

(华为-2019-芯片-数字-34) 从后端设计考虑,在必须使用门控时钟的时候,需要遵循一个原则:门控时钟的输出只能跟着时钟信号进行跳变,而不能跟着控制信号进行跳变,也就是说对于用N…

数字IC前端学习笔记:数字乘法器的优化设计(基4布斯编码华莱士树乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 使用基2布斯乘法器虽然能减少乘数中0的数量,但最终还是无法减少部分积的数量,因此一种更合理的编码方式产生了——基4布斯编码。它可以将部…

【VCS Verdi】VCS Verdi 联合仿真总结

1. VCS 介绍VCS是编译型 Verilog 模拟器,它完全支持 OVI 标准的 Verilog HDL 语言、PLI 和 SDF。VCS 具有行业中较高的模拟性能,其出色的内存管理能力足以支持千万门级的 ASIC 设计,而其模拟精度也完全满足深亚微米 ASIC Sign-Off 的要求。VC…

Aurora 8B/10B - Clock and Reset

目录 1. Clock and Reset Interface2. Duplex Power On and Reset Sequences2.1. Automatic Reset by hard errorSource Code2.2. Duplex Normal Manul Reset Sequences2.3. Duplex Power On Manul Reset Sequences2.4. Core Partners Reset Deadlock1. Clock and Reset Interf…

design rules check: S rules

Scannability Rules (S Rules)

根据library cells和pre-existing scan segments进行scan substitution和stitching。

对于library cells来说,一个简单的cell可能只包括单个memory element,存在non-scan版本和等价的扫描版本。在这种情况下,必须在memory element上执行S-ru…

一段来自《Verilog HDL 高级数字设计》的错误Verilog代码

笔者之前在阅读《Verilog HDL 高级数字设计》时的基4布斯乘法器一文时,就遇到了一段有问题的代码,而这个问题可以用Verilog基础:表达式位宽的确定(位宽拓展)文中的分析完美解决。

always (negedge clock) if (Start)…

Verilog基础:$random系统函数的使用

相关阅读

Verilog基础编辑https://blog.csdn.net/weixin_45791458/category_12263729.html $random系统函数语法的BNF范式如下所示,有关BNF范式相关内容,可以浏览以往文章Verilog基础:巴科斯范式(BNF)。 $random系统函数在每次调用时返回一…

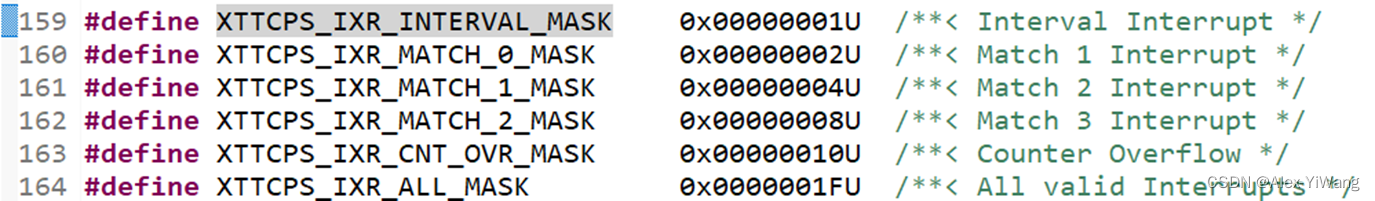

ZYNQ:【1】深入理解PS端的TTC定时器(Part1:原理+官方案例讲解)

碎碎念:好久不见,甚是想念!本期带来的是有关ZYNQ7020的内容,我们知道ZYNQ作为一款具有硬核的SOC,PS端很强大,可以更加便捷地实现一些算法验证。本文具体讲解一下里面的TTC定时器,之后发布的Part…

数字IC芯片验证流程及验证工具推荐?收藏专用

验证其实是一个“证伪”的过程,从流程到工具,验证工程师的终极目的都只有一个:

发现所有BUG,或者证明没有BUG,以保证芯片功能性能的正确性和可靠性。

验证环节对于一颗芯片的重要性也是不言而喻的:

从项…

【SystemVerilog】数据类型(3)数组的方法

目录

一、数组缩减方法

二、数组定位方法

三、数组排序方法 SV提供了很多数组的方法,可用于任何一种非合并的数组类型,包括定宽数组、动态数组、队列和关联数组。这些方法有繁有简,简单的如求当前数组的大小,复杂的如对数组排序…

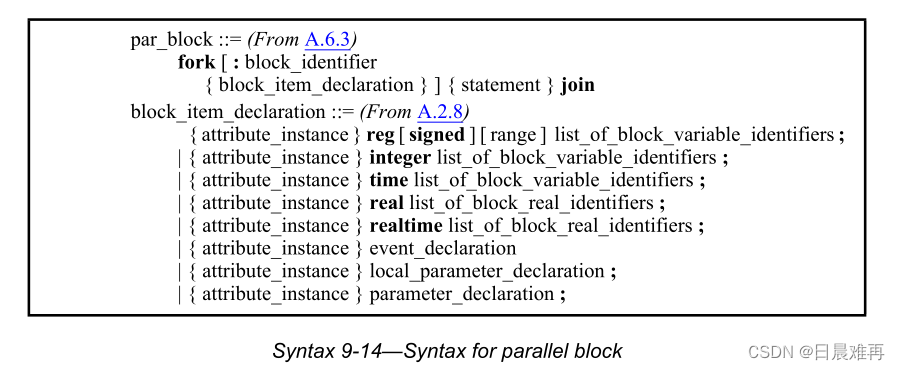

Verilog基础:块语句

相关阅读

Verilog基础专栏https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 1、块语句 块语句(block statements)是一种把语句组织在一起,这样他们在语法上就像单个语句一样工作。Verilog HDL中有两种类型的块: …

入行IC | 一文读懂FPGA与ASIC的区别

IC行业的范围很广,有数字、模拟不同的研究方向,也有设计、制造、封测不同的产业环节、还有FPGA、ASIC等不一样的芯片领域。

遇到过很多想要入行、转行IC的同学,都有“选FPGA还是ASIC”的问题。区分概念往往是做选择的前提,所以首…

【数字IC/FPGA】什么是无符号数?什么是有符号数?

进制

虽然在日常生活中,我们已经习惯了使用10进制数字,但在由数字电路构成的数字世界中,2进制才是效率更高的选择。

10进制与2进制

10进制(decimal)计数法(一般也叫阿拉伯计数法)是在日常生活…

IC设计行业都有哪些不错的公司(外企篇)

当越来越多的同学选择IC修真院之后,咨询的问题就从最开始的该怎么入行IC设计,慢慢变成了该怎么选择offer,该怎么挑选公司?

非科班的同学本就对IC行业知之甚少,更别提具体的公司状况,他们不清楚为什么不推荐…

转行IC的人都会问到的五个问题

随着IC设计的“出圈”,无论是行业发展还是薪资涨幅,都算得上盛名在外了。现在很多非微电子科班的理工科专业的同学都想转行芯片行业,大量求职者的涌入使得企业的用人门槛和工作强度逐渐变高。

经过一年的“转行潮”,越来越多的同…

给微电子专业学生的一些建议,如何避免踩坑?

建议往往都是有时效性的,就拿高考报志愿来说,20年前的土木专业的那套说法并不适用于今天,也说不准10年后最好的专业可能真的是“生化材环”。

当下来说,微电子专业无疑是志愿选择中较为优秀的方向,但如果仅仅把时间往…

微电子专业深度盘点:哪所大学芯片最强?强在哪?(第2弹)

众所周知,国内高校微电子专业都以示范性28所微电子学院为代表,其中又分前9所和后19所,之间的区别就在于:

前9所是支持建设示范性微电子学院,后19所是支持筹备建设示范性微电子学院。建设与筹备建设之间的区别很容易理…

科普 | IC工程师到底有哪些?(设计+制造)

随着摩尔定律和技术的发展,芯片集成度也越来越高,与之伴随的就是岗位愈加细分。芯片产业链很长且环环相扣,每一个环节都需要不同的工程师角色分工协作。

很多人以为芯片工程师就是单纯搞芯片的工程师,殊不知这其中可能要分十几个…

学员追访丨器件转行IC的一点心得分享

图片

大家好,我是验证十期学员L,一个中科院微电子所的器件硕士,理论上来说,算是原本想学微电子,结果还是进了材料的坑。目前通过转行IC,现在已经拿到某企业芯片验证工程师的offer,年薪33W。

这…

Pipeline Stages

Use of Pipeline Stages in the Compactor

Pipeline stages有时能够通过提高扫描移位频率来提高数据通过compactor中逻辑的整体速率。pipeline stages是通过logic level保持中间值输出的寄存器,所以进入logic level中的值可能在一个时钟周期中更早地更新。因为EDT逻辑逻辑级数…

数字SOC设计之低功耗设计入门(二)——功耗的分析

前面学习了进行低功耗的目的个功耗的构成,今天就来分享一下功耗的分析。由于是面向数字IC前端设计的学习,所以这里的功耗分析是基于DC中的power compiler工具;更精确的功耗分析可以采用PT,关于PT的功耗分析可以查阅其他资料&#…

【SystemVerilog】SV对设计意图的细化always和unique/priority

always、always_comb、always_latch、always_ff;

unique /priority case ; unique /priority if...else ; 一、SV中的always

在Verilog中,设计组合逻辑和时序逻辑时,都要用到always:

always (*)begin…

数字ic设计自学ing

绝对零基础开始┭┮﹏┭┮

1、数字电子技术基础

学习视频:

中国大学mooc 数字电子技术 北京科技大学

中国大学moocVLSI设计基础(数字集成电路设计基础)东南大学

2、学习芯片开发所需要的环境

Linux环境

编译器:Vim脚本语言…

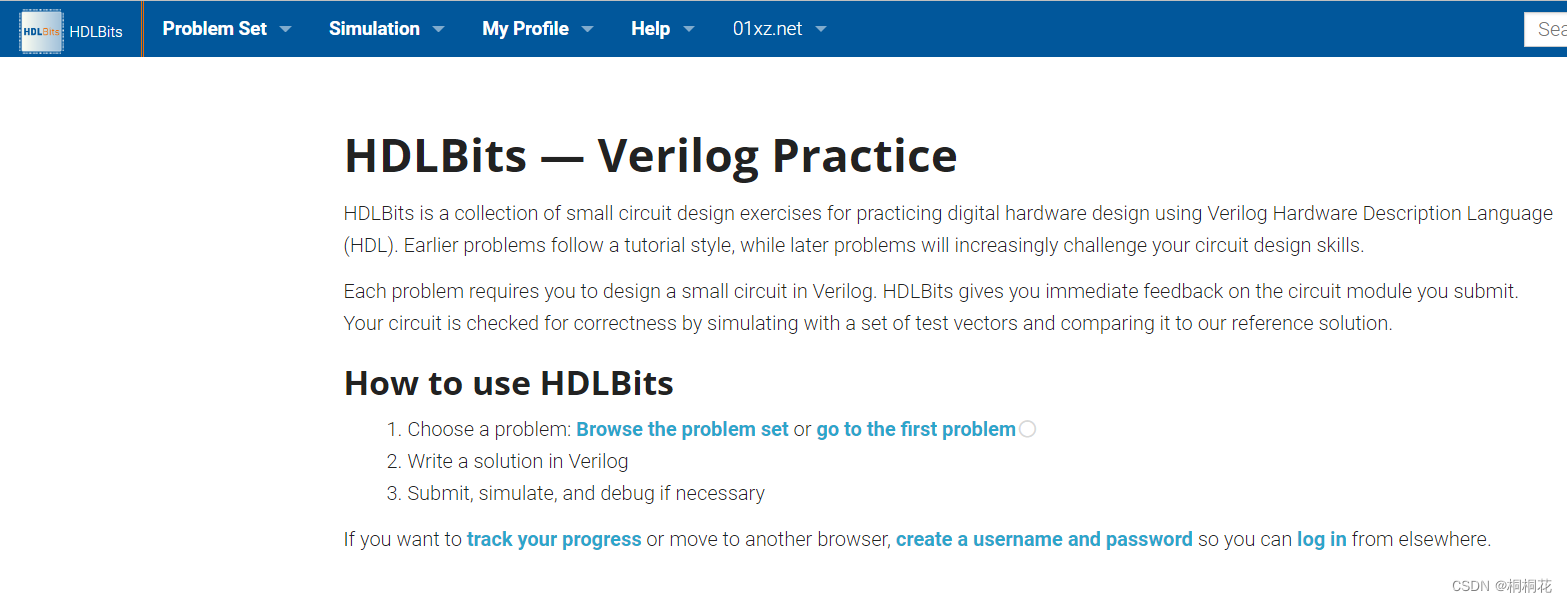

运算电路(1)——加法器

一、引言 微处理器是由一片或少数几片大规模集成电路组成的中央处理器。这些电路执行控制部件和算术逻辑部件的功能。微处理器能完成取指令、执行指令,以及与外界存储器和逻辑部件交换信息等操作,是微型计算机的运算控制部分。它可与存储器和外围电路芯片…

【数字IC/FPGA】书籍推荐(1)----《轻松成为设计高手--Verilog HDL实用精解》

在下这几年关于数字电路、Verilog、FPGA和IC方面的书前前后后都读了不少,发现了不少好书,也在一些废话书上浪费过时间。接下来会写一系列文章,把一部分读过的书做个测评,根据个人标准按十分制满分来打分分享给大家。 书名…

【Verilog】CRC校验码生成器原理及verilog实现

目录

一、CRC的基本原理 二、CRC生成步骤

2.1举个栗子

三、Verilog实现

四、参考资料

4.1 CRC在线计算器 一、CRC的基本原理

CRC :Cyclic Redundancy Check循环冗余校验码 将被处理的报文比特序列当做一个二进制多项式A(x)的系数,任意一个由二进制…

【从零开始学习 UVM】12.3、UVM RAL(续更) —— RAL Classes Methods

文章目录 uvm_reg_blockuvm_reg_block methodsuvm_reguvm_reg methodsuvm_reg_fielduvm_reg_field 访问策略uvm_reg_field methodsuvm_reg_fileuvm_reg_file methodsuvm_memuvm_mem methodsuvm_reg_mapuvm_reg_map methods设置单个map的相关sequencer和ada

DFT设计中相关词汇

1.Automatd Test Equipment(ATE)

自动测试和分析功能参数的设备,以此来评估被测试的电子设备的性能。

2.Automatic Test Pattern Generator(ATPG)

program生成的一种process,要求test patterns为设计产生高故障覆盖率。

3.Blackbox

不存在的instanc…

静态时序分析:SDC约束命令set_disable_timing详解

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html 目录

指定对象列表

指定源、目的引脚

指定恢复

简单使用

写在最后 上一章中,我们学习了如何使用set_case_analysis模式分析命令,它通过指定某个端口或引脚为固定值&…

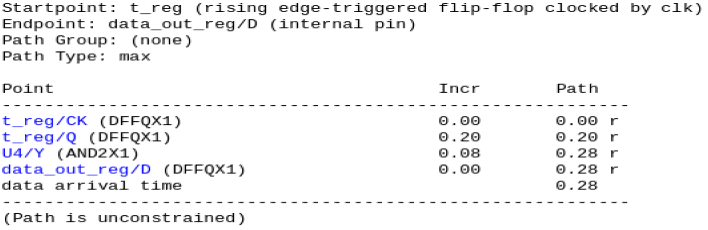

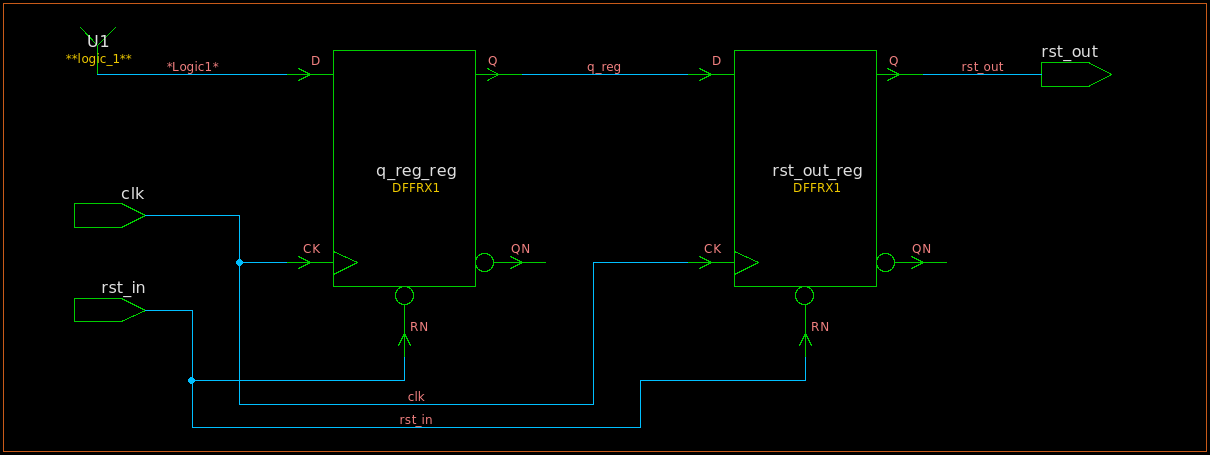

数字IC前端学习笔记:异步复位,同步释放

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 异步复位 异步复位是一种常见的复位方式,可以使电路进入一个可知的状态。但是不正确地使用异步复位会导致出现意想不到的错误,复位释放便是…

数字IC前端学习笔记:仲裁轮询(四)

相关文章

数字IC前端学习笔记:LSFR(线性反馈移位寄存器)

数字IC前端学习笔记:跨时钟域信号同步

数字IC前端学习笔记:信号同步和边沿检测

数字IC前端学习笔记:锁存器Latch的综合

数字IC前端学习笔记&am…

8B/10B Transmission Code

目录 1. Overview2. 8B/10B Endcoding2.1. Running Disparity2.3. Ordered Sets2.4. Idle Sequence3. 8B/10B Decoding4. Clock Compensation5. Striping介绍8B/10B编码的原理及相关数据流 sp002 - Aurora 8B/10B protocol spec 8B/10B编码原理详解、Verilog实现及在JESD204B中…

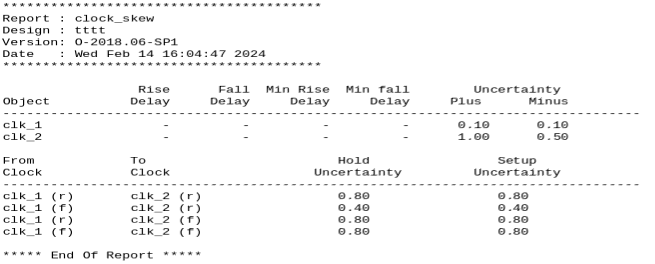

静态时序分析:SDC约束命令set_clock_uncertainty

相关阅读

静态时序分析https://blog.csdn.net/weixin_45791458/category_12567571.html?spm1001.2014.3001.5482 set_clock_uncertainty是用来指定设计中时钟周期的不确定性,不确定性指的是对那些会对时钟周期造成的负面影响。这些不确定性可能来源于时钟抖动(clo…

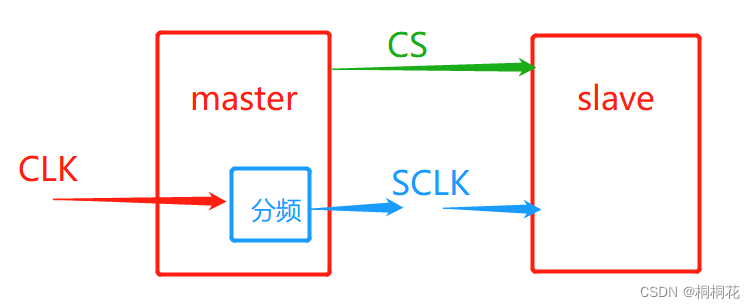

数字ic设计——SPI

SPI总线概念 SPI ( Serial Peripheral Interface,串行外围设备接口)是一种同步、全双工、主从式,高速接口(UART是异步)。 来自主机或 从机 的数据在时钟上升沿或下降沿同步。主机和从机可以同时传输数据。 串行外设接…

数字ic设计——UART

UART定义 UART 的全称是通用异步收发器(Universal Asynchronous Receiver/Transmitter),是实现设备之间低速数据通信的标准协议。 是一种通用的串行、异步通信总线。 该总线有两条数据线,可以实现全双工的发送和接收在嵌入式系统中…

【数字IC前端笔试真题精刷(2022.7.28)】芯动——数字IC验证工程师(1号卷-验证)

笔试时间:2022-7-28; 题目类型: 不定项(10x1’=10’)【错选不得分,少选得1/3分】问答(9x10’=90’)文章目录 不定项1、(单选)在verilog语言中,a=4b1011,那么&a=()2、(单选)System Verilog 中类默认的成员属性是 ()3、(单选)在Verilog中定义了宏名define sum atb+…

【从零开始学习 UVM】12.6、UVM RAL(续更) —— RAL Predictor

文章目录 隐式(自动)预测显式预测在TestBench环境中的插件reg_predictor被动预测UVM RAL 预测器是一个组件,它基于物理接口上的transaction更新镜像值,UVM 提供了“uvm_reg_predictor”基类。

DUT 寄存器可以通过 RAL 方法(如读取和写入)或在目标agent上运行具有有效地址…

【System Verilog基础】automatic自动存储--用堆栈区存储局部变量

文章目录一、C语言的内存分配:BSS、Data、Text、Heap(堆)、Stack(栈)1、1、静态内存分配:BSS、Data1、2、程序执行代码:Text1、3、动态内存分配:Heap(堆)、St…

【从零开始学习 UVM】7.1、Driver Sequencer Handshake —— Driver 与 Sequencer 的握手机制

文章目录 sequencer如何与driver通信?为什么我们需要driver sequencer API 方法?driver中的TLM port叫什么?sequencer中的TLM port叫什么?一个driver如何连接到sequencer?sequencer如何与driver通信?

driver类包含一个名为uvm_seq_item_pull_port的TLM端口,该端口连接到…

【UVM实战练习项目】3、UVM验证环境基本框架搭建(实例二)(隐式启动sequence、加入新数据包、加入factory覆盖)

本文的实例二相对于上一篇的实例一有以下变化:

实例二在env中采用了default_sequence隐式的方式启动sequence发送数据,不同于上文中的start显式方式启动;实例二中添加了新的数据包,该包继承原来的包,增补了约束&#…

笔试题-2023-AMD-芯片设计【纯净题目版】

回到首页:2023 数字IC设计秋招复盘——数十家公司笔试题、面试实录 推荐内容:数字IC设计学习比较实用的资料推荐

题目背景 笔试时间:2022.09.12应聘岗位:芯片设计工程师 ASIC Design Engineer笔试时长:60min笔试平台:ShowMeBug题目类型:单选题(15道)、多选题(6道)、…

IC行业秋招真实情况记录,快来看看吧~

2023年,IC行业人才竞争尤为激烈。为了更好的获取到面试的经验,不妨先来了解一下IC面试常见的问题,以及面试该准备的相关事项吧~

(文末可领全部面试题目)

什么是同步逻辑和异步逻辑?

同步逻辑是时钟之间…

SystemVerilog基础:并行块fork-join、join_any、join_none(二)

相关阅读

SystemVerilog基础https://blog.csdn.net/weixin_45791458/category_12517449.html 在第一节中,我们讨论了并行块中的fork-join块和fork-join_any块,了解了它们的差异,本文将继续讨论fork-join_none块的使用。 fork-join_none并行块…

Verilog基础:$time、$stime和$realtime系统函数的使用

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html $time、 $stime和$realtime这三个系统函数提供了返回当前仿真时间方法。注意,这里的仿真时间的最小分辨能力是由仿真时间精度决定的,简单来说,可以理解为…

【SpinalHDL快速入门】4.1、基本类型之Bool

Tips1: 由于SpinalHDL是基于Scala构建的,Scala本身自带类似变量Boolean,故在此要认准SpinalHDL中采用的是Bool而非Boolean:

Bool(大写的True和False):True表示1,False表示0Boolean&…

为什么很多人从FPGA转IC前端岗?哪个前景好?

很多入行不久的朋友潜意识里会认为FPGA是很高深的东西,能掌握FPGA的一定都是极其厉害的人。

其实,这是一个误解。

我们所讨论的FPGA只是基于已有的FPGA芯片去做后端排列组合的工作内容,而不是设计制造新的FPGA芯片,世界上能做这…

Verilog基础:时序调度中的竞争(二)

相关阅读

Verilog基础https://blog.csdn.net/weixin_45791458/category_12263729.html?spm1001.2014.3001.5482 作为一个硬件描述语言,Verilog HDL常常需要使用语句描述并行执行的电路,但其实在仿真器的底层,这些并行执行的语句是有先后顺序…

【数字IC设计】利用Design Compiler评估动态功耗

利用DC对RTL设计的动态功耗进行评估,主要可以分为以下步骤: 用vcs编译运行testbench,生成.saif文件(Switching Activity Interchange Format)在Design Compiler编译前,读入.saif文件Design Compiler编译完设计文件后,输出功耗报告 下面通过一个计数器的设计,来演示该过程…

【从零开始学习 UVM】10.7、UVM TLM —— TLM Fifo [uvm_tlm_fifo]

文章目录 UVM TLM FIFO Example1. 创建一个发送器类,其端口类型为 `uvm_blocking_put_port`2. 创建接收器类,使用 get 方法进行接收。3. 通过高层次的 TLM FIFO 连接这两个组件假设发送方的数据速率比接收方获取数据包的速率快得多。需要在两者之间插入一个FIFO元素来存储数据…

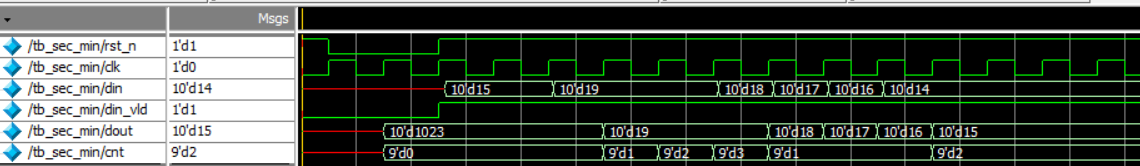

【Verilog基础】RTL设计指导原则(面积与速度互换、模块复用、串并转换、乒乓操作(乒乓buffer)、流水线操作)

文章目录 一、RTL设计指导原则二、面积与速度的平衡与互换原则三、速度换面积:模块复用四、面积换速度:串并转换五、面积换速度:乒乓操作六、面积换速度:流水线操作(Pipeline)6、1、为啥加入流水线可以提高频率?七、问题讨论一、RTL设计指导原则 1、RTL (Register Tran…

【数字IC基础】半导体存储器(Semi-conductor Memory):静态存储器SRAM、动态存储器DRAM、只读存储器ROM

文章目录 一、半导体存储器(Semi-conductor Memory)二、随机读写存储器RAM(Random Access Memory)2、1、SRAM(Static RAM)静态存储器2、2、DRAM(Dynamic RAM)动态存储器2、3、EDRAM增强型DRAM三、只读存储器ROM(Read Only Memory)3、1、MROM 掩膜只读存储器3、2、PROM …

数字IC手撕代码--乐鑫科技(次小值与次小值出现的次数)

前言:本专栏旨在记录高频笔面试手撕代码题,以备数字前端秋招,本专栏所有文章提供原理分析、代码及波形,所有代码均经过本人验证。目录如下:1.数字IC手撕代码-分频器(任意偶数分频)2.数字IC手撕代…

静态时序分析(Static Timing Analysis, STA):内容导航

目录1. 介绍1.1. 局限性2. STA基本元素3. STA标准单元库4. STA环境5. STA时序检查6. STA接口分析7. STA鲁棒性检查静态时序分析(Static Timing Analysis, STA)是用来验证数字设计时序的技术之一,也是数字IC设计者必备的设计技能。

本专栏blo…

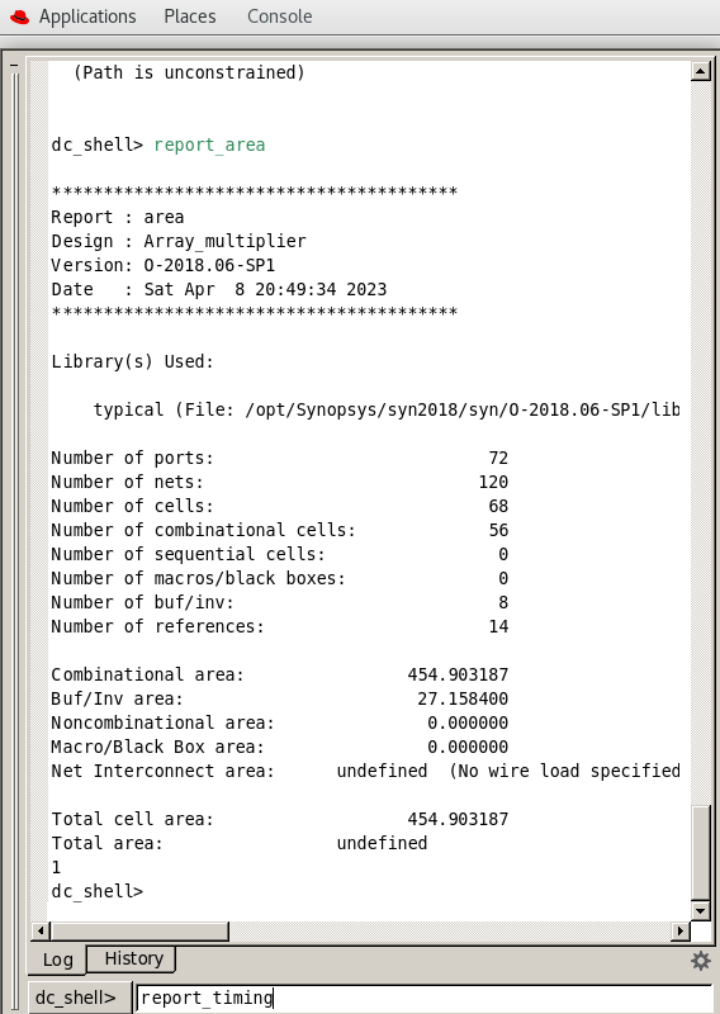

数字IC前端学习笔记:数字乘法器的优化设计(阵列乘法器)

相关阅读

数字IC前端https://blog.csdn.net/weixin_45791458/category_12173698.html?spm1001.2014.3001.5482 数字信号处理作为微处理器的核心部件,是决定着总体处理器性能的因素之一,而数字乘法器是最常见的一种数字信号处理电路。通常情况下&#…

数字IC前端学习笔记:仲裁轮询(五)

相关文章

数字IC前端学习笔记:LSFR(线性反馈移位寄存器)

数字IC前端学习笔记:跨时钟域信号同步

数字IC前端学习笔记:信号同步和边沿检测

数字IC前端学习笔记:锁存器Latch的综合

数字IC前端学习笔记&am…

海康威视 2024届 数字逻辑设计 实习笔试分析

说明

记录一下 5月11日晚,做的海康威视的一场笔试。分享给需要的IC人。

岗位:数字逻辑设计工程师(浙江 杭州)

转载需要本人同意!

我的见解不一定都是准确的,欢迎评论区交流指正~~ 单选题

1、ÿ…

【从零开始学习 UVM】11.5、UVM Register Layer —— 后门访问 实战项目(RAL实战,交通灯为例)

文章目录 后门访问是什么?定义后门 HDL 路径示例sequence中的后门访问示例UVM寄存器模型允许使用前门访问DUT寄存器,就像我们之前在寄存器环境中看到的那样。

这意味着环境中的所有寄存器读写操作都会转换为总线事务,并驱动到设计的总线接口,就像典型系统中的任何其他硬件…

数字IC设计方法学:内容导航

目录1. 介绍2. 技能篇● Verilog● 数字电路基础● 时钟复位设计● 亚稳态设计● 低功耗设计● Systemverilog● Linux● TCL● VCS● Python/C● SVN3. 技术篇● RTL Design Flow● 综合逻辑综合工具Design Compile(DC)形式验证工具Formality时序分析工…

![【从零开始学习 UVM】3.5、UVM TestBench架构 —— UVM Sequencer [uvm_sequencer]](https://img-blog.csdnimg.cn/195f597a6bbf4ea78fbacf540fed2476.png)

![【从零开始学习 UVM】10.7、UVM TLM —— TLM Fifo [uvm_tlm_fifo]](https://img-blog.csdnimg.cn/441de33cb39147a681d61705a3314fcc.png)